# AKAI

Multisystem LCD TV set

**LTA-32N658HCP**

**LTA-32N680HCP**

**LTC-26N680HCP**

**LTC-32N680HCP**

Service manual

# LCD COLOUR TV

# SERVICE MANUAL

**MODEL:**

**LTC-26N680HCP**

**LTC-32N680HCP**

**LTA-32N680HCP**

**LTA-32N658HCP**

**CHASSIS NO. : LS02/PS02**

*Please read this manual carefully before service.*

# Catalog

|                 |                                                                                  |           |

|-----------------|----------------------------------------------------------------------------------|-----------|

| <b>Chapter1</b> | <b>Specifications and Composition .....</b>                                      | <b>4</b>  |

| <b>Chapter2</b> | <b>Function Introduction of Main IC .....</b>                                    | <b>7</b>  |

| <b>Chapter3</b> | <b>Analysis of Signal process Flowchart and key point<br/>measure date .....</b> | <b>31</b> |

| <b>Chapter4</b> | <b>Maintenance Procedure and Examples of Typical<br/>troubleshooting .....</b>   | <b>40</b> |

| <b>Chapter5</b> | <b>Spare Part Lists.....</b>                                                     | <b>42</b> |

| <b>Chapter6</b> | <b>Factory Setup and notice.....</b>                                             | <b>43</b> |

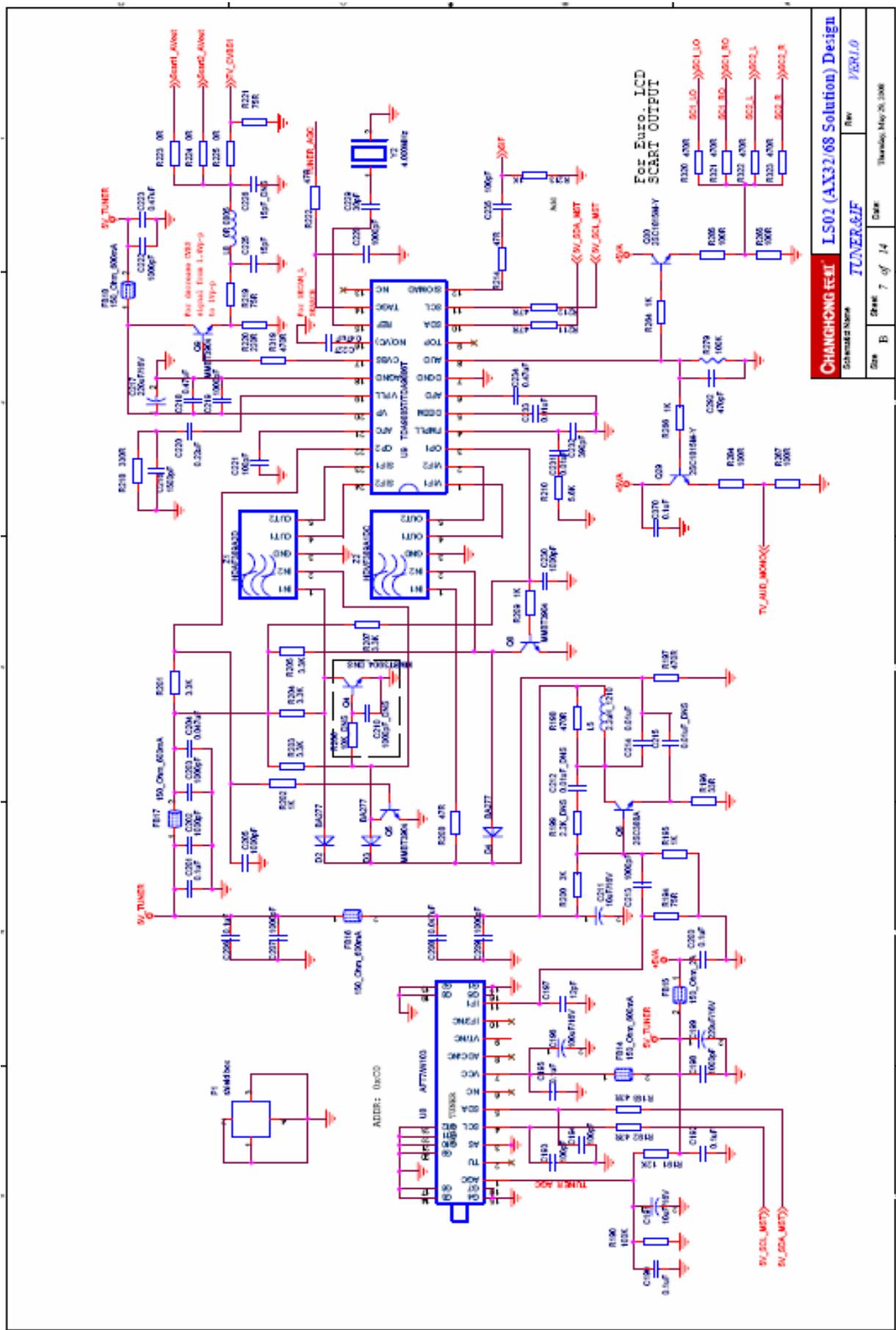

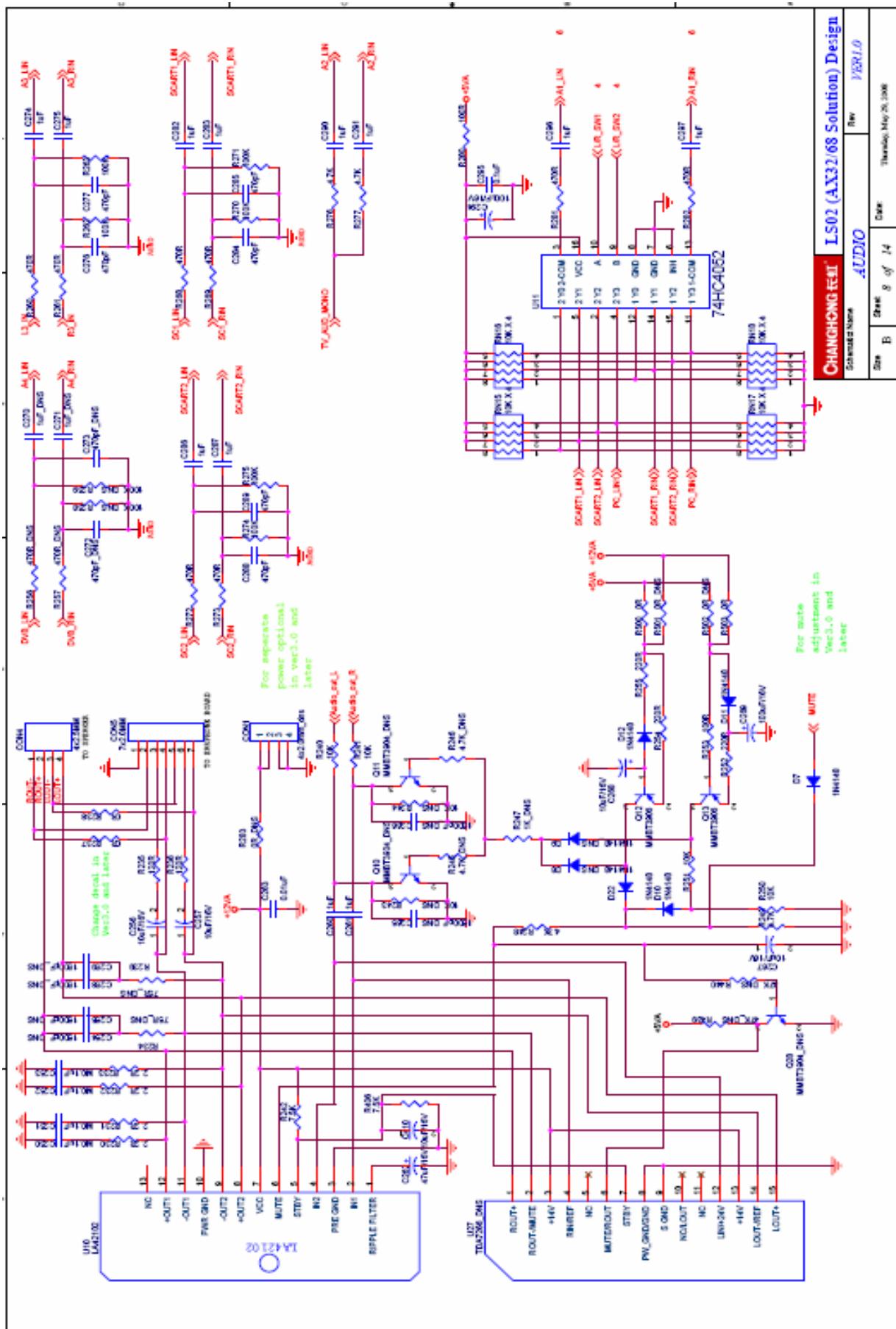

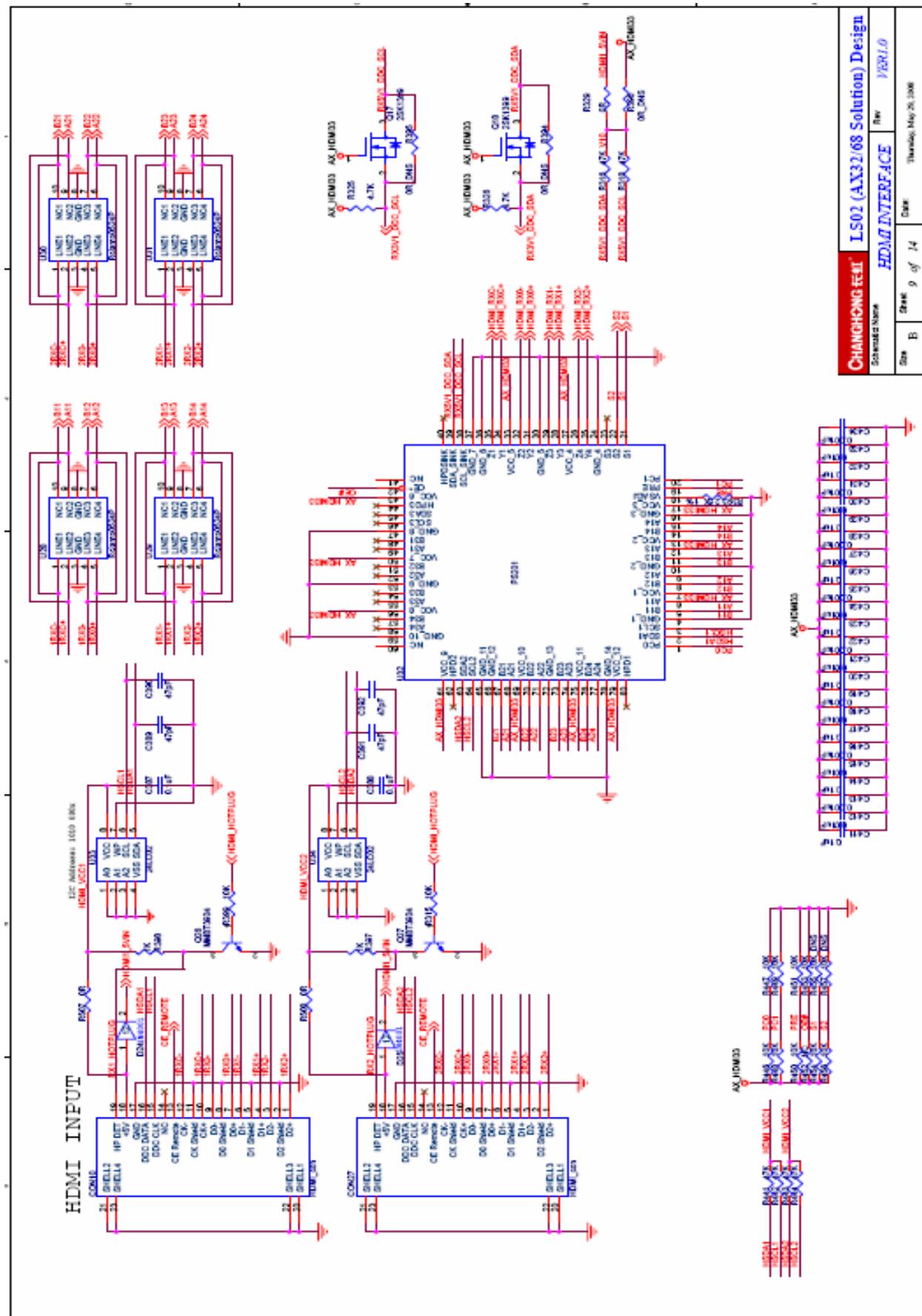

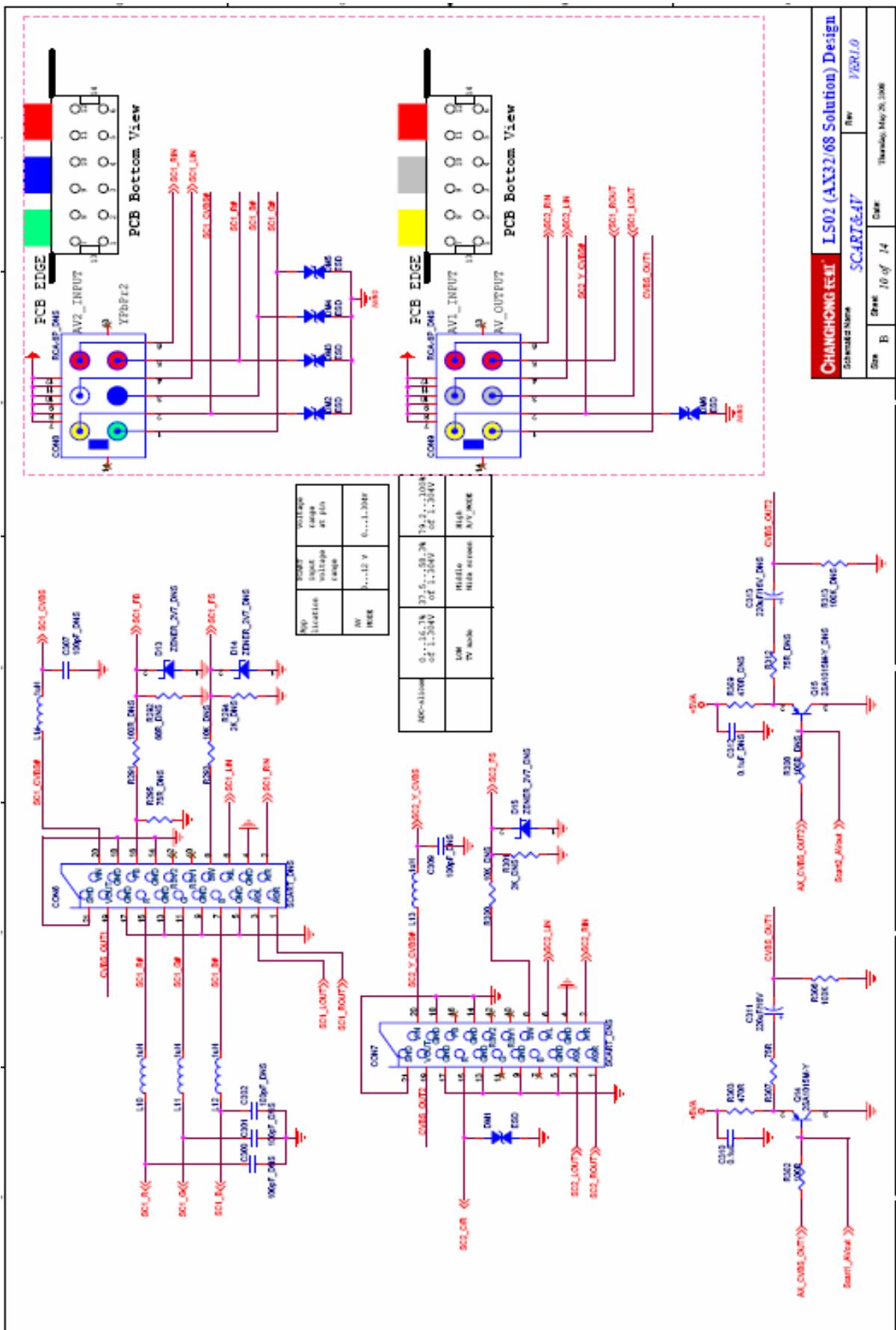

**Appendix: Circuit Schematic diagram**

# Chapter 1: Specifications and Composition

## 1. Models for LS02/PS02 chassis :

| Region          | Europe                 | America                | Other regions          |

|-----------------|------------------------|------------------------|------------------------|

| Original Models | LT26GHxxE              | LT37GHxxE              | LT26GHxxA              |

|                 | LT32GHxxE              | LT42GHxxE              | LT37GHxxA              |

|                 | LT47GHxxE              | LT47GHxxU              | LT32GHxxA              |

|                 | xx:01,19,29,30,41 etc. | xx:01,19,29,30,41 etc. | LT42GHxxA              |

|                 | PT32GHxxE              | PT42GHxxE              | LT47GHxxA              |

|                 | PT50GHxxE              | PT50GHxxU              | xx:01,19,29,30,41 etc. |

|                 | xx:218,528,26,18,36    | xx:218,528,26,18,36    | PT32GHxxA              |

|                 |                        |                        | T42GHxxA               |

|                 |                        |                        | PT50GHxxA              |

|                 |                        |                        | xx:218,528,26,18,36    |

## 2. Main Feature

| Region                            | Europe                                                                                                                  | America                                   | Other regions                         |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------|

| RF signal                         | Color system                                                                                                            | PAL、SECAM                                 | NTSC、PAL M/ N                         |

|                                   | Sound system                                                                                                            | D/K、B/G、I、L/L'                            | M/N                                   |

| Video or Y/C signal               | PAL、NTSC、SECAM                                                                                                          | PAL、NTSC、SECAM                            | PAL、NTSC、SECAM                        |

| Program presetting                | 100 (0-235)                                                                                                             | 181 (AIR: 2-69; CABLE: 1-125)             | 236 (0-235)                           |

| Audio output (THD≤7%)             | 5W+5W                                                                                                                   | 5W+5W                                     | 5W+5W                                 |

| Power source                      | 100V~240V                                                                                                               | 100V~240V                                 | 100V~240V                             |

| Teletxt                           | 100 pages                                                                                                               | X                                         | 100 pages                             |

| CCD                               | X                                                                                                                       | Yes                                       | X                                     |

| VCHIP                             | X                                                                                                                       | Yes                                       | X                                     |

| Sound demodulator                 | NICAM、IGR                                                                                                               | BTSC                                      | NICAM、IGR                             |

| SCART                             | Yes                                                                                                                     | X                                         | X                                     |

| VGA                               | Yes                                                                                                                     | Yes                                       | Yes                                   |

| YPbPr                             | Yes                                                                                                                     | Yes                                       | Yes                                   |

| HDMI                              | Yes                                                                                                                     | Yes                                       | Yes                                   |

| Earphone                          | Yes                                                                                                                     | Yes                                       | Yes                                   |

| OSD language                      | English, French, German, Italian, Portuguese etc.                                                                       | English, French, Portuguese, Spanish etc. | English, French, German, Spanish etc. |

| Auto Off without Signal Reception | 5 minutes                                                                                                               |                                           |                                       |

| Program booking                   | 5 program booking. Turn to the corresponding program at the booking time.                                               |                                           |                                       |

| Swap                              | Customer could rearrange the channels according to personal habit                                                       |                                           |                                       |

| Plug and Play                     | LCD TV could be used as computer screen, no need for the installation of software, which is Plug and Play in real sense |                                           |                                       |

## 3. Unit IC Compositions:

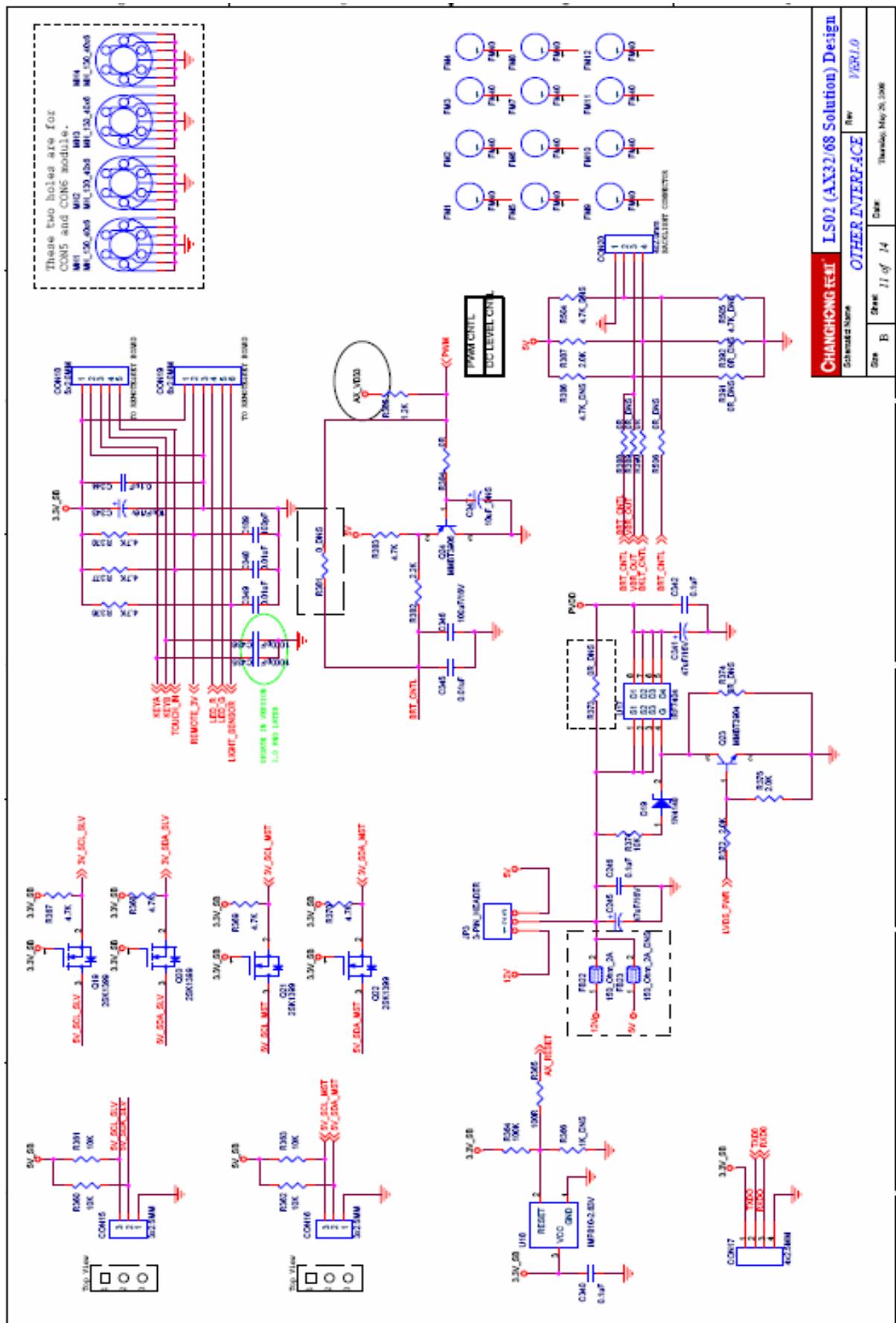

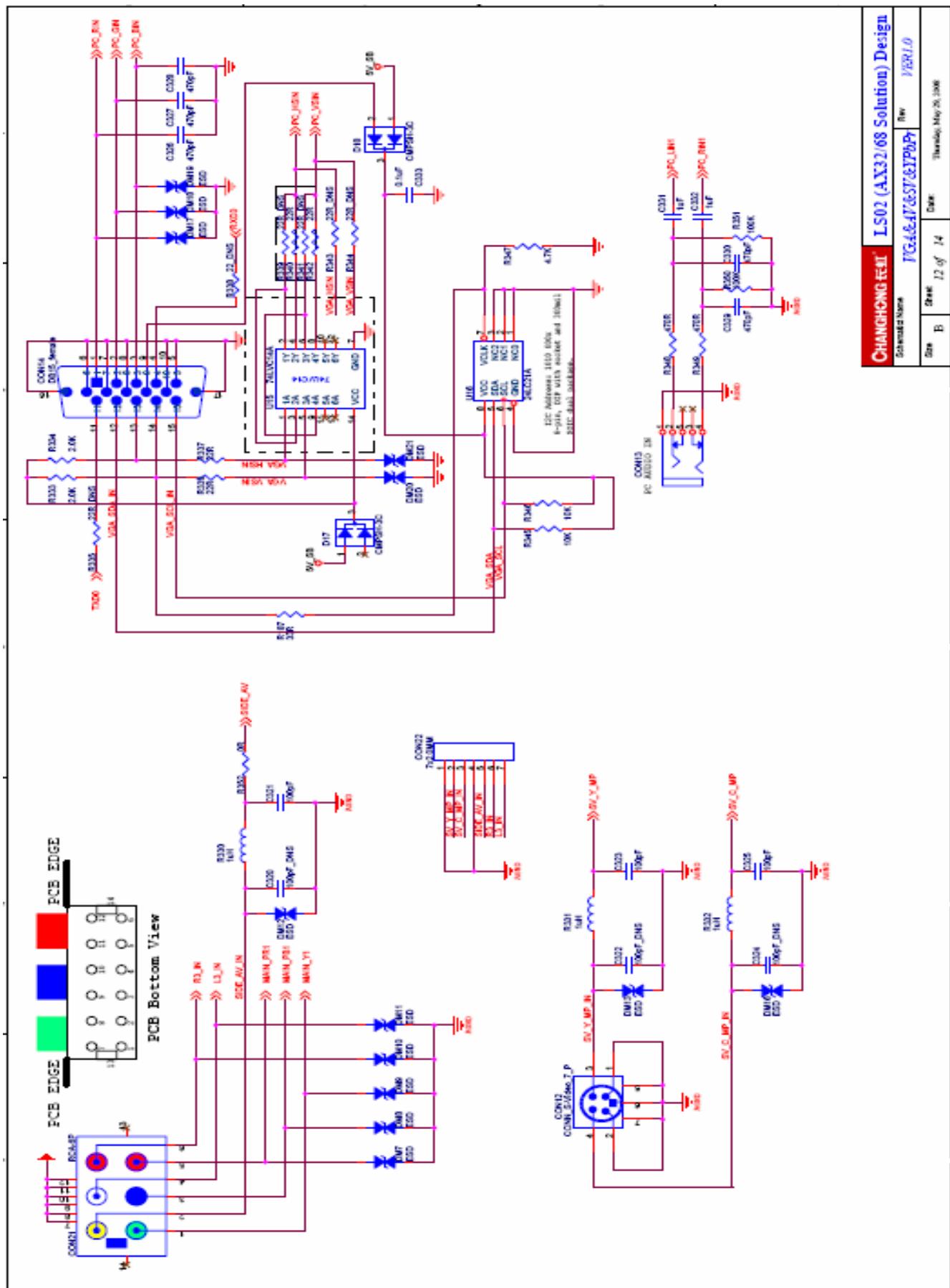

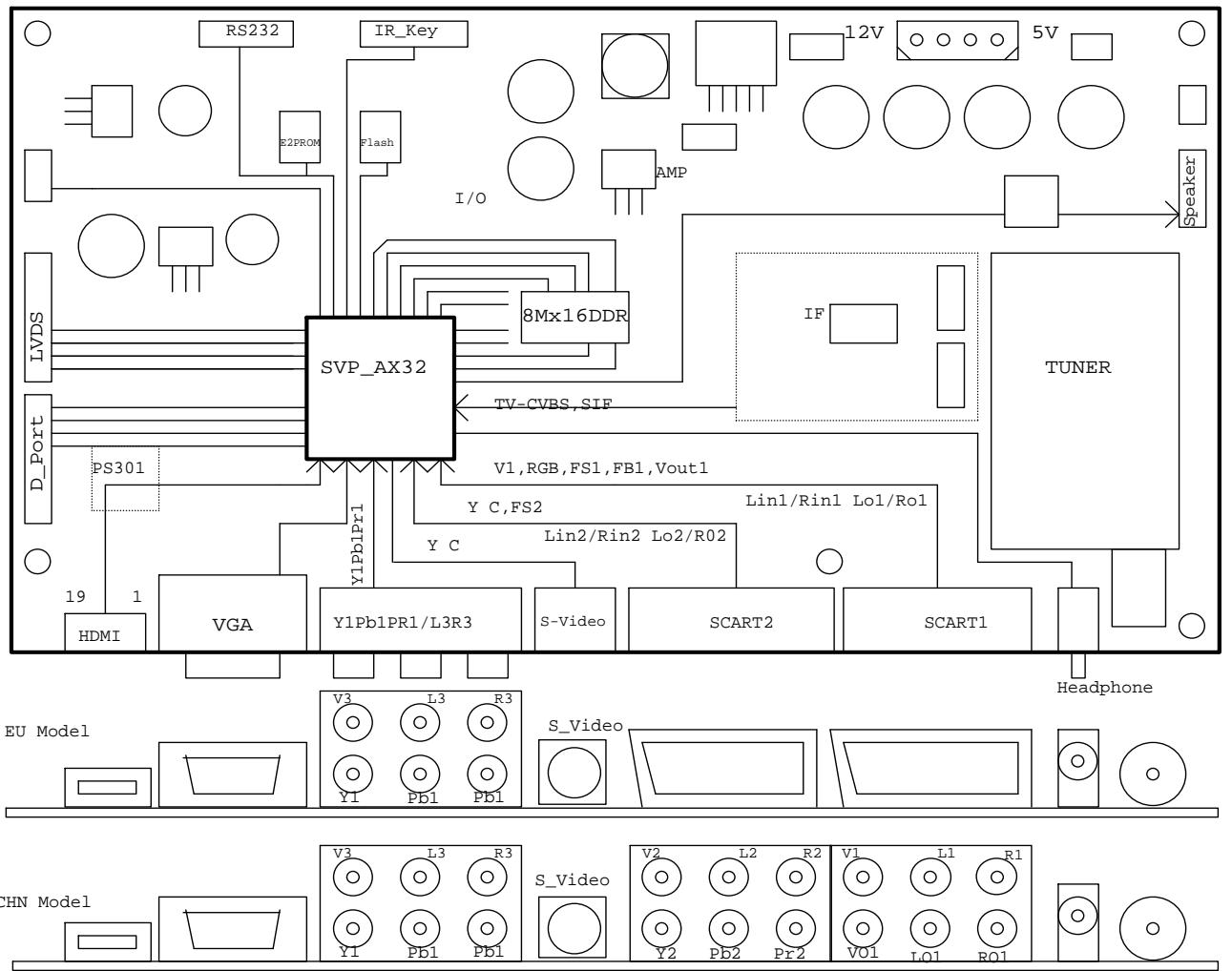

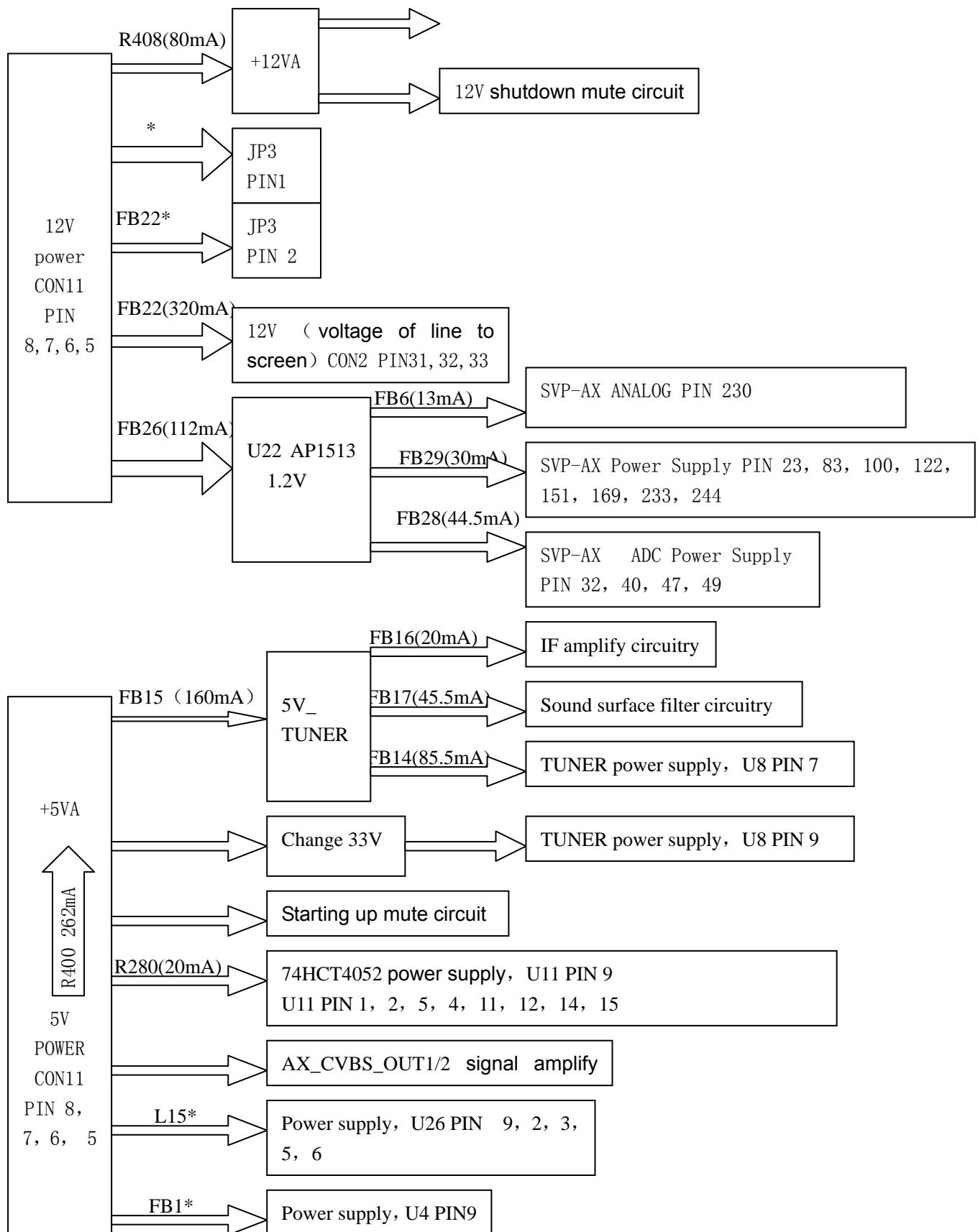

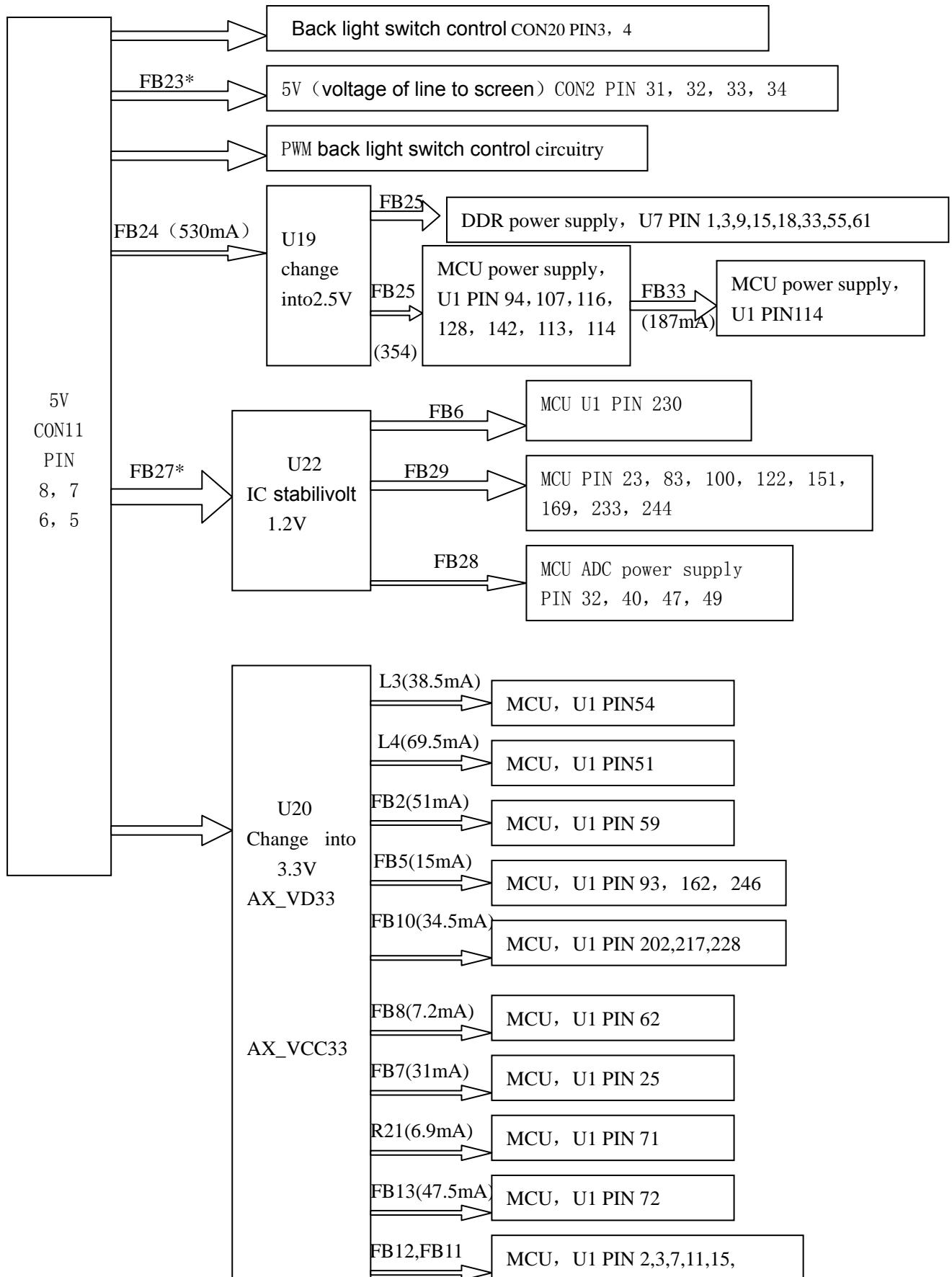

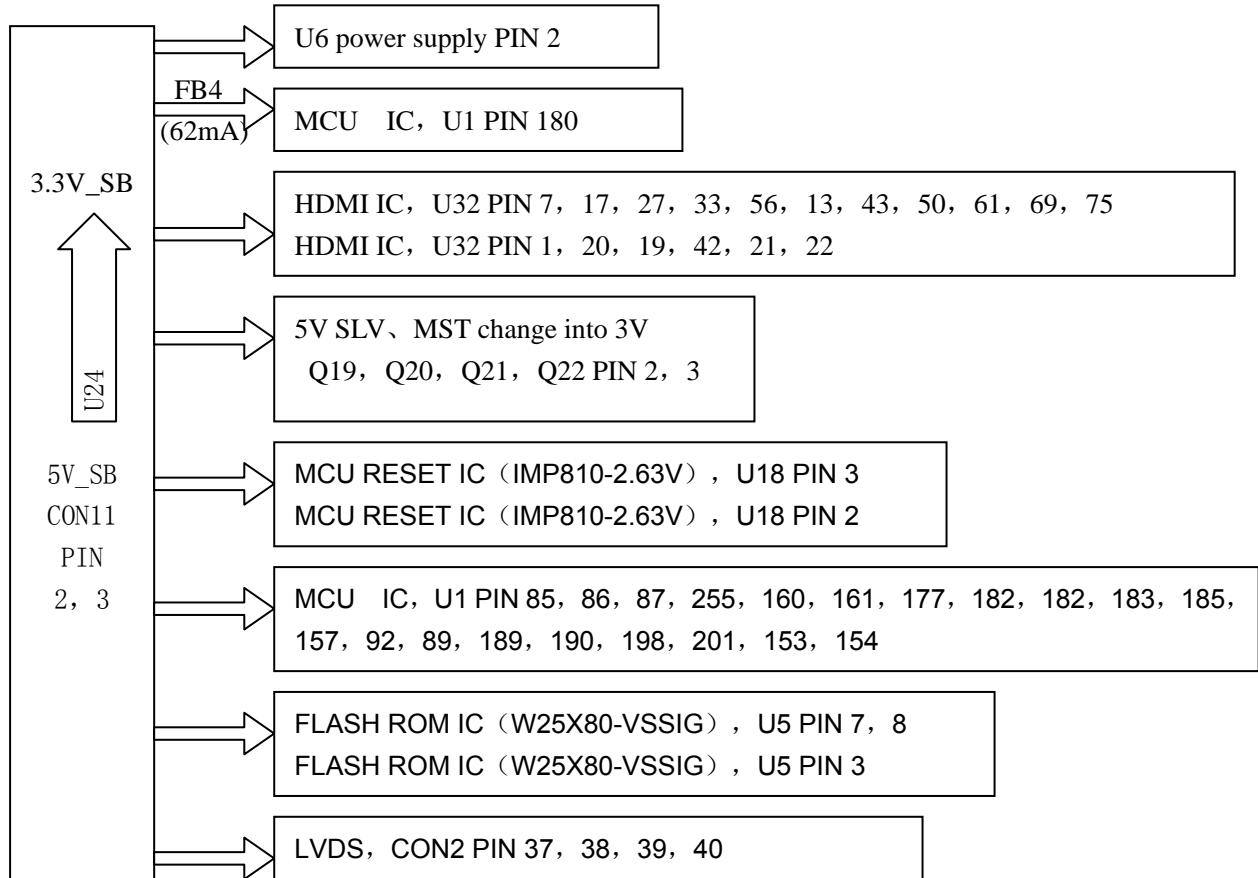

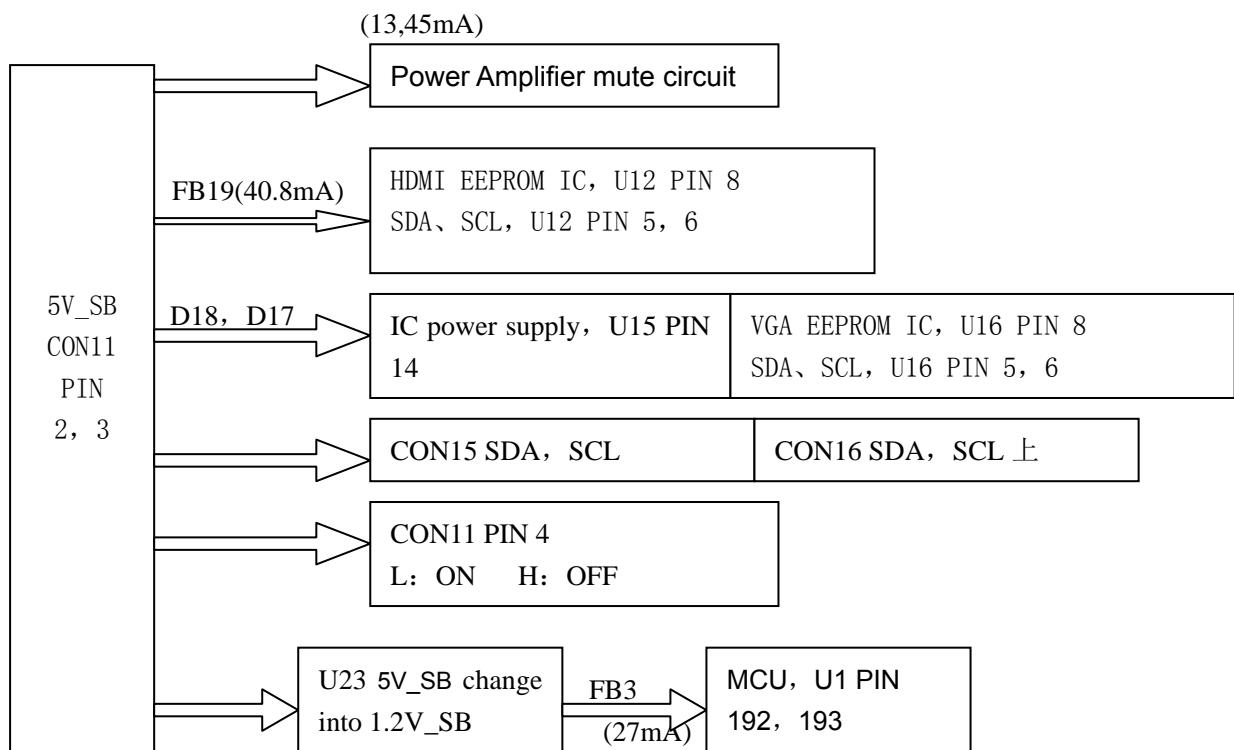

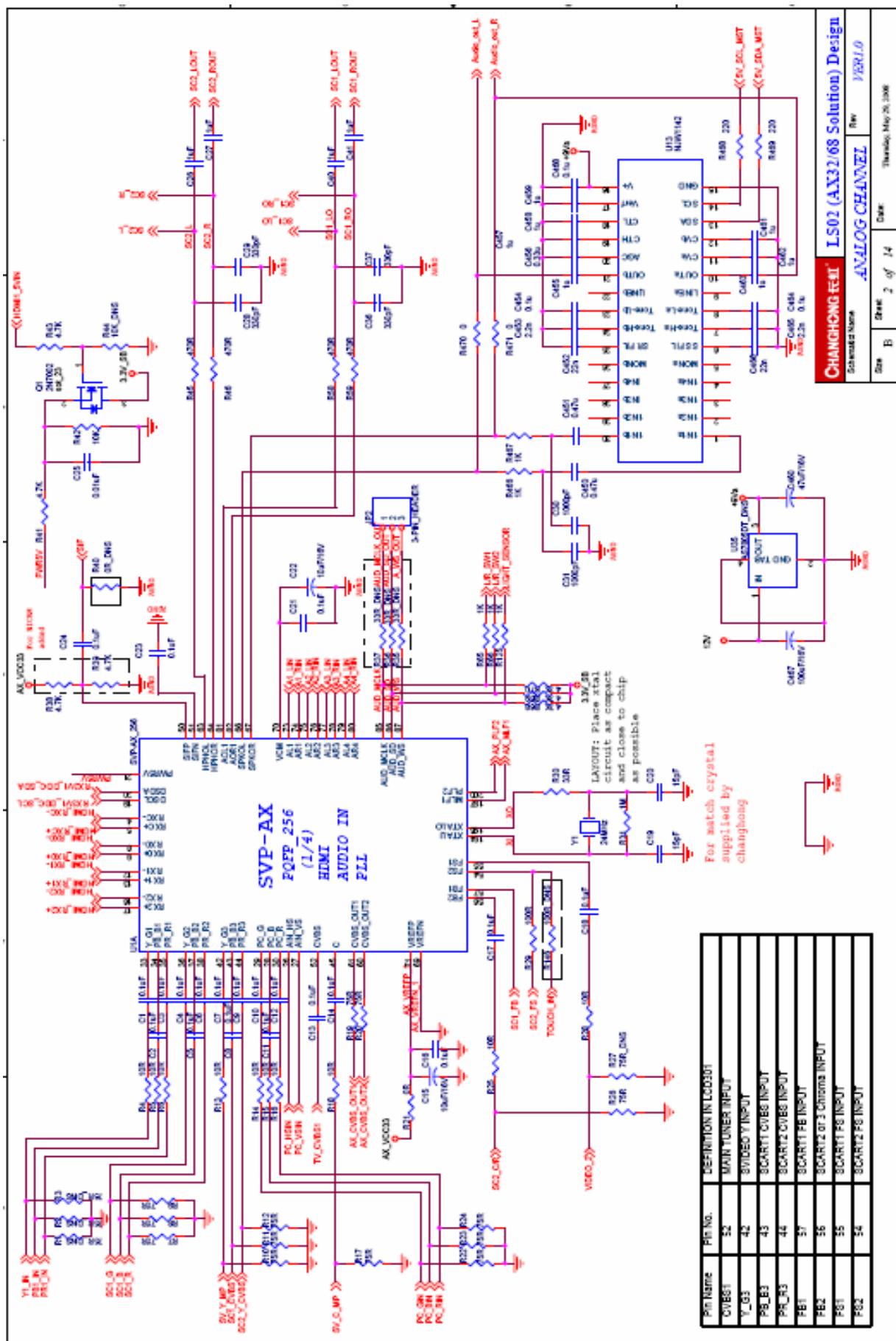

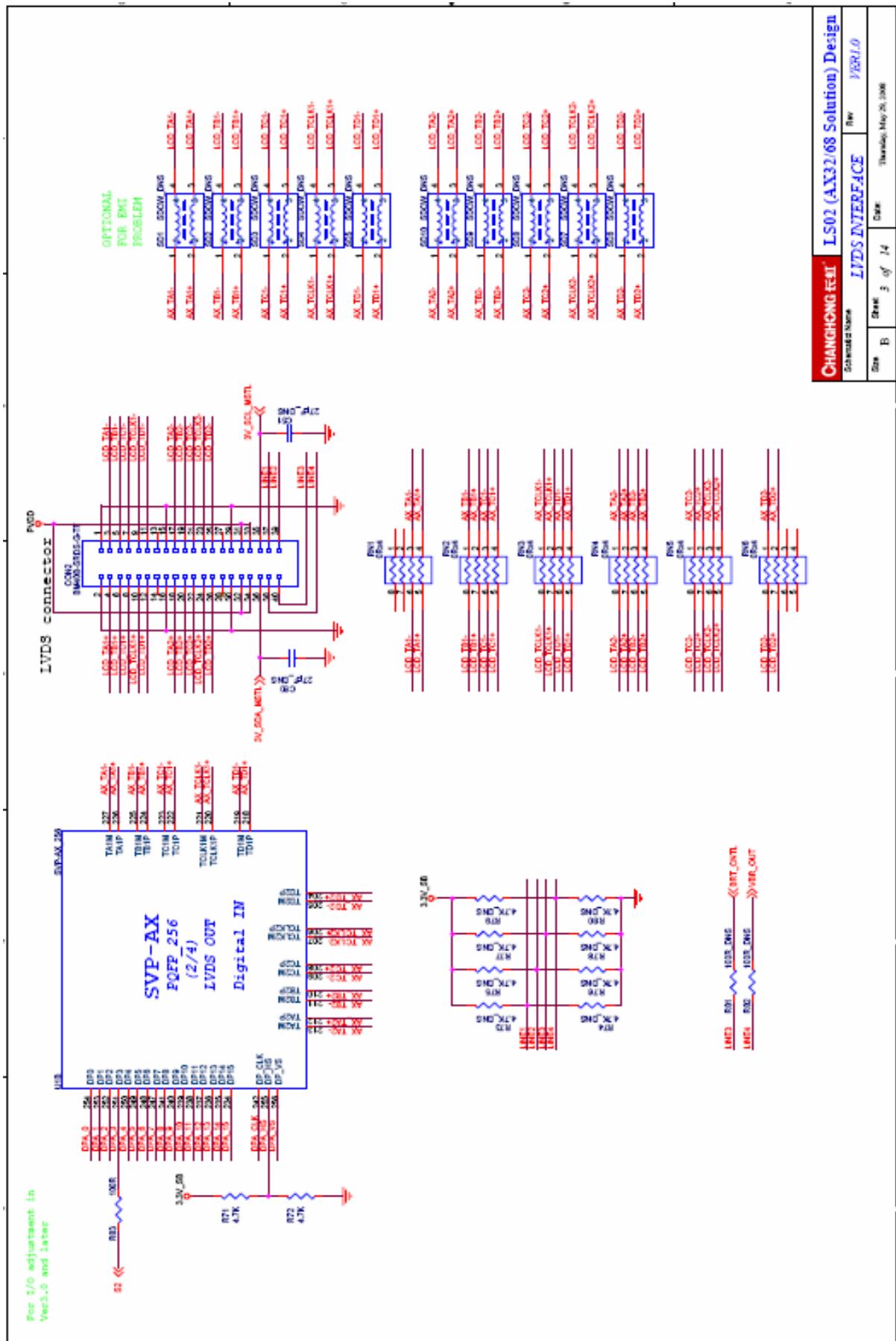

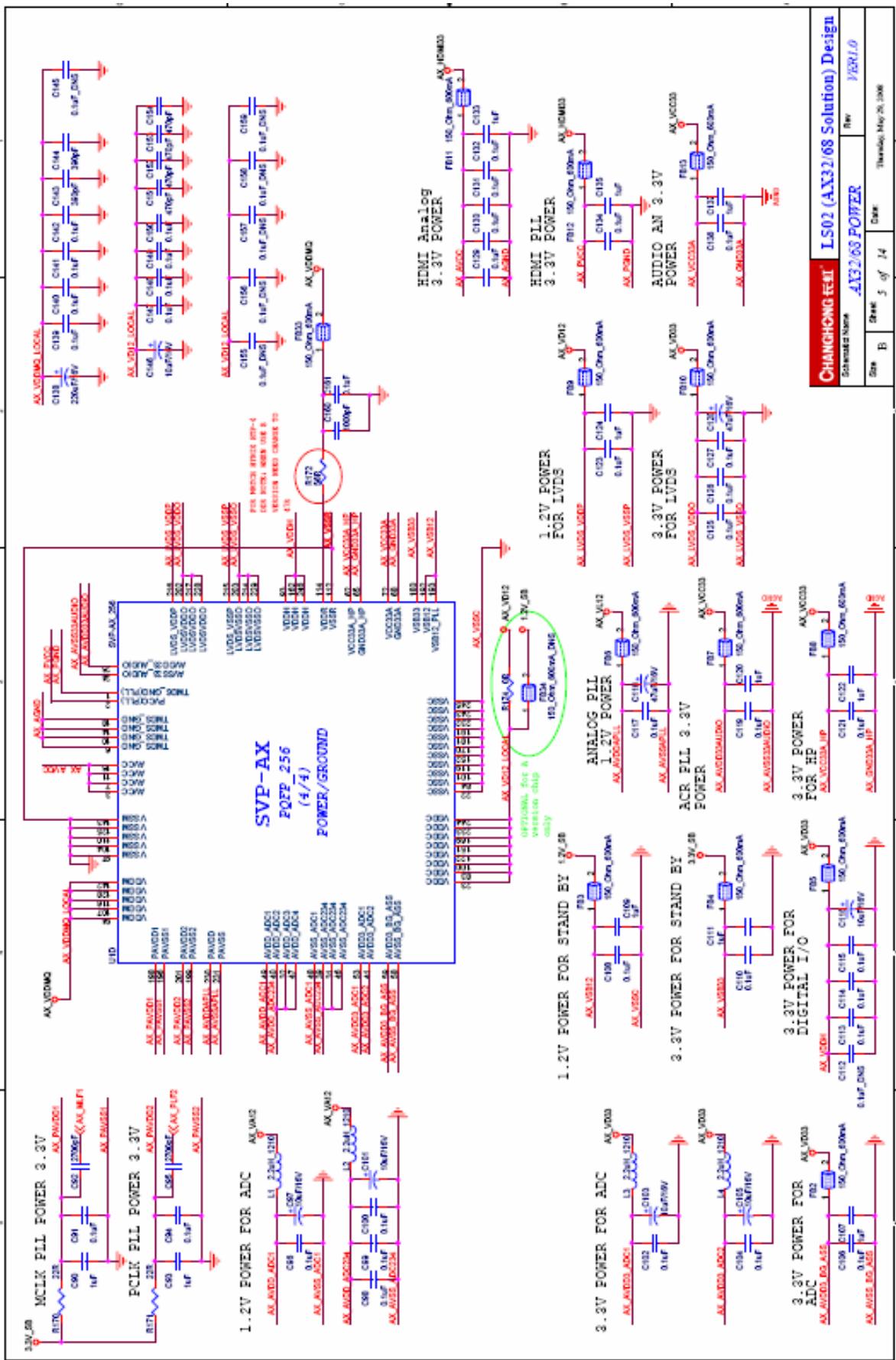

LCD TV with LS02/PS02 chassis is made up of switch power, system control circuit, video processing circuit, audio processing circuit, Power Amplifier circuit, AV input circuit, LCD screen module. Block circuit diagram is shown as below:

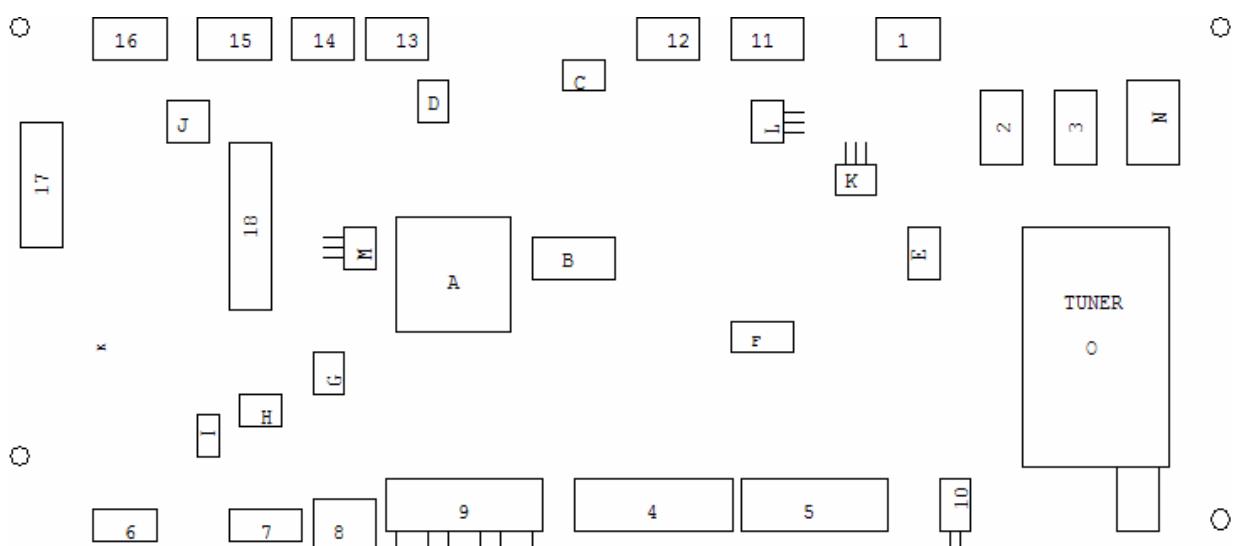

#### 4. Introduction of PCB module

LCD TV with LS02/PS02 Chassis is made up of power board, side AV board, remote control reception board, key board, and mainboard. The table below is the introduction of the function of all printed board modules.

| No. | Parts                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Mainboard module            | Mainboard module is the core of LCD TV signal processing. Under the control of the system control circuit, It undertakes the task of converting the external input signal into the unified digital signal that the LCD screen could identify. Mainboard controls the whole machine through IIC bus, decode VIDEO signal, controls the Video (brightness, contrast, chroma, hue, definition etc), white balance adjusts, generates OSD, de-interlaces signal, converts signal frequency, and finishes signal A/D and D/A conversion, video enhancement, LVDS signal coding and output; it has Scart , S-Video, AV , YPbPr, HDMI and PC interface, Tuner input, sound demodulation, sound processing, sound power amplifier, and online update. |

| 2   | Remote reception module     | The remote reception board module is constituted by an indicator-light and a remote reception. Customer could manipulate the LCD TV by using remote controller very conveniently. By the color of the indicator light, the operation mode of the LCD TV could be judged (red is standby, green is power on).                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3   | Built-in power board module | Convert the 100V~240V (50/60HZ) AC into DC, output have +12V, +5V, +3.3V and the +5V_STB in standby state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4   | Keyboard module             | Keyboard module has 7 function keys (program +/-, volume +/-, AV/TV, menu ,power), customer could use the key to operate the TV freely.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5   | LCD screen module           | LCD screen has built-in inverter that convert DC into high voltage AC signal to turn on the backlight CCFL (Cold Cathode Fluorescent Light); the LCD screen process the video signal from signal board and reappear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | Side board AV               | Side AV board is used for earphone output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## Chapter 2: Function Introduction of Main IC

### 1. Main ICs and functional modules of LS02/PS02 chassis

| No. | Item no. | Model                               | Main function                                                                                                                                                                                                                                                                       |

|-----|----------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | U8       | AFT7/W003<br>AFT7/W103<br>AFT7/W300 | Tuner, output sound IF and video signal                                                                                                                                                                                                                                             |

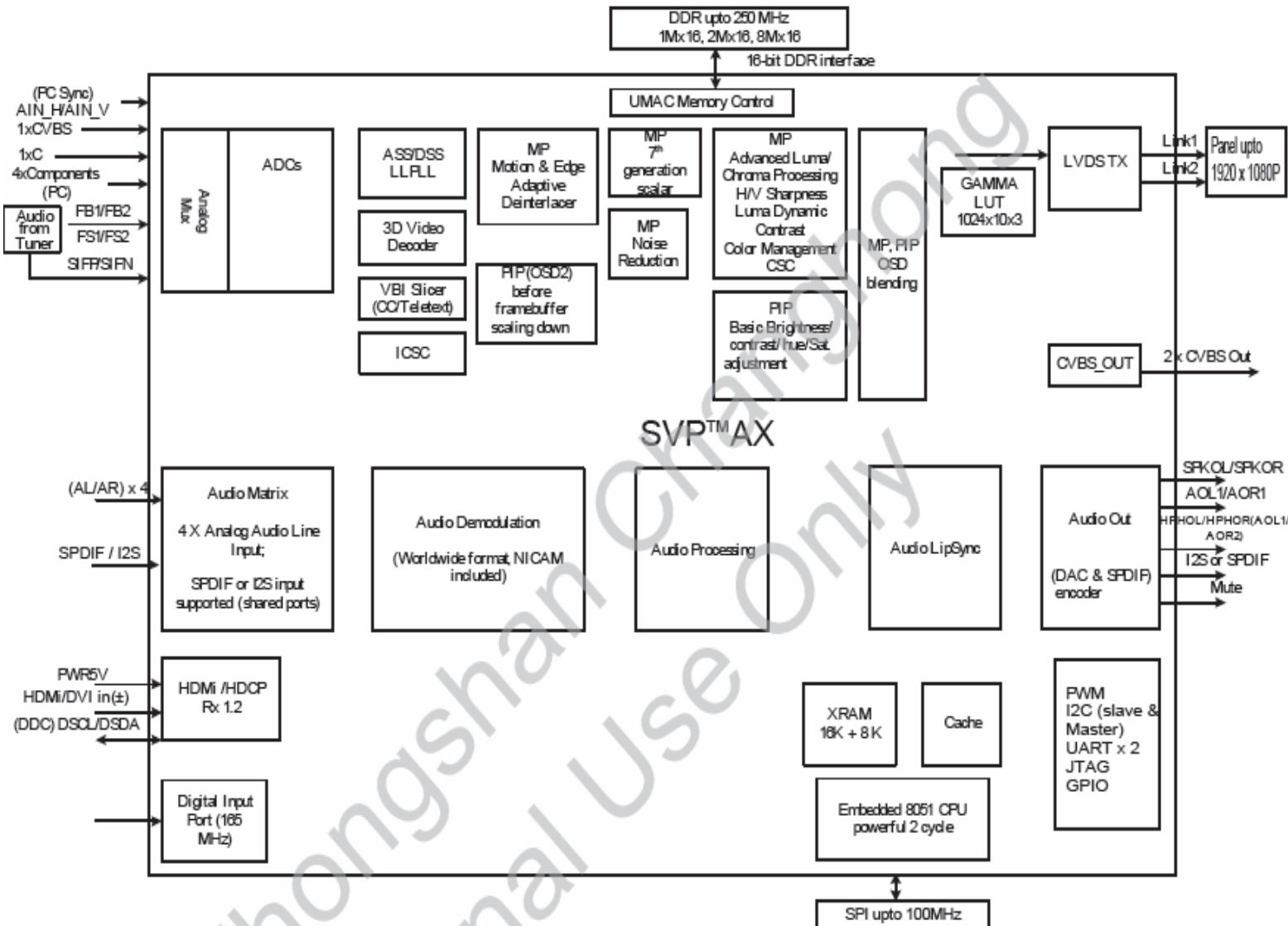

| 2   | U1       | SVP-AX32LF/SVP-AX68LF               | SVP AX family video processors provide the highest performance, target the converging HDTV-ready and PC-ready LCD TV, PDP TV applications where high precession processing of video, which Embed in ADC converter、3D comb filter、HDMI processor、video decoder、LVDS transmitter etc. |

| 3   | U3       | AT24C64-SO8-DNS                     | EEPROM                                                                                                                                                                                                                                                                              |

| 4   | U5       | W25X80-VSSIG                        | 8M-bit Serial Flash, Store the Control program.                                                                                                                                                                                                                                     |

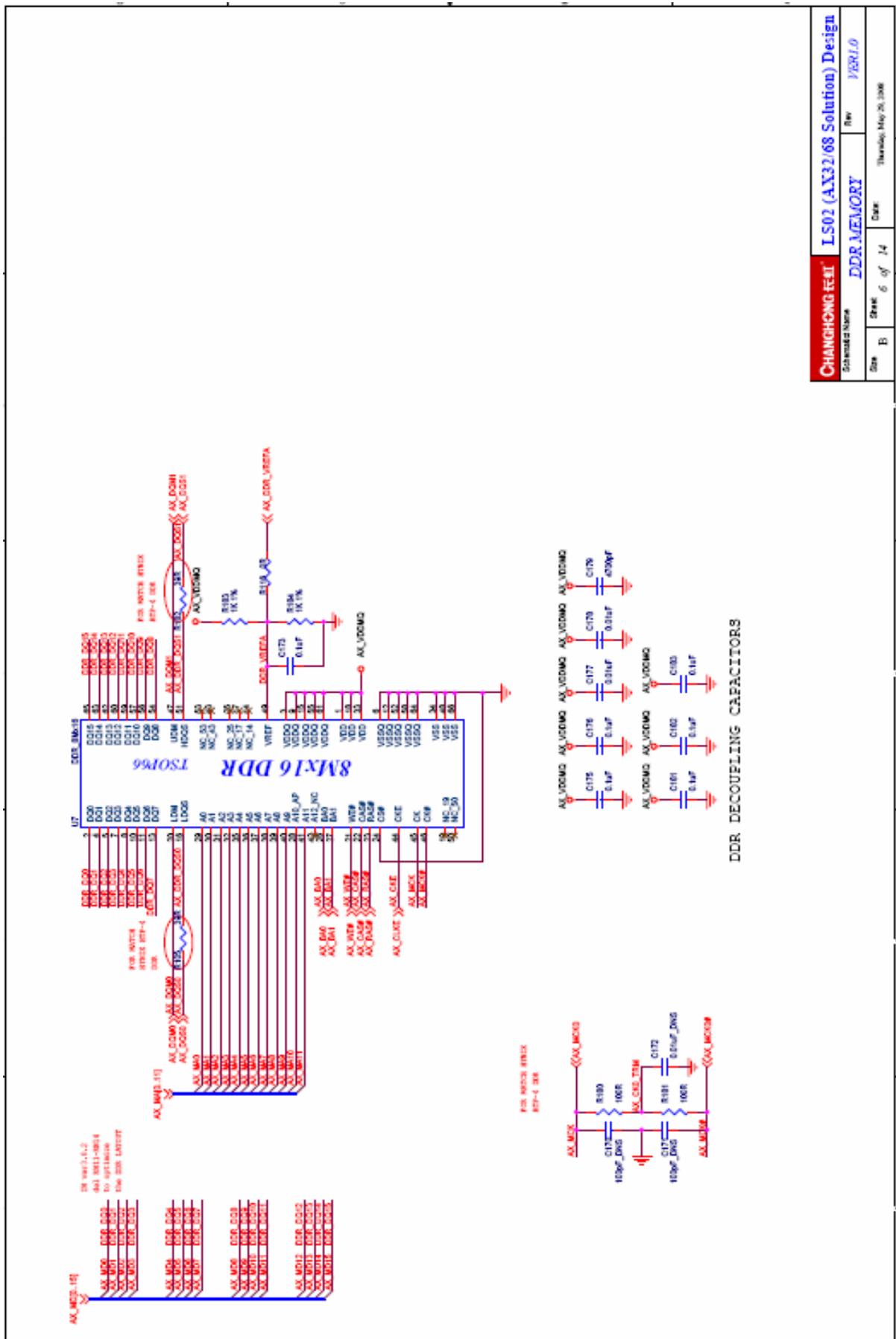

| 5   | U7       | HY5DU281622FTP-4                    | 8M×16bits DDR SDRAM                                                                                                                                                                                                                                                                 |

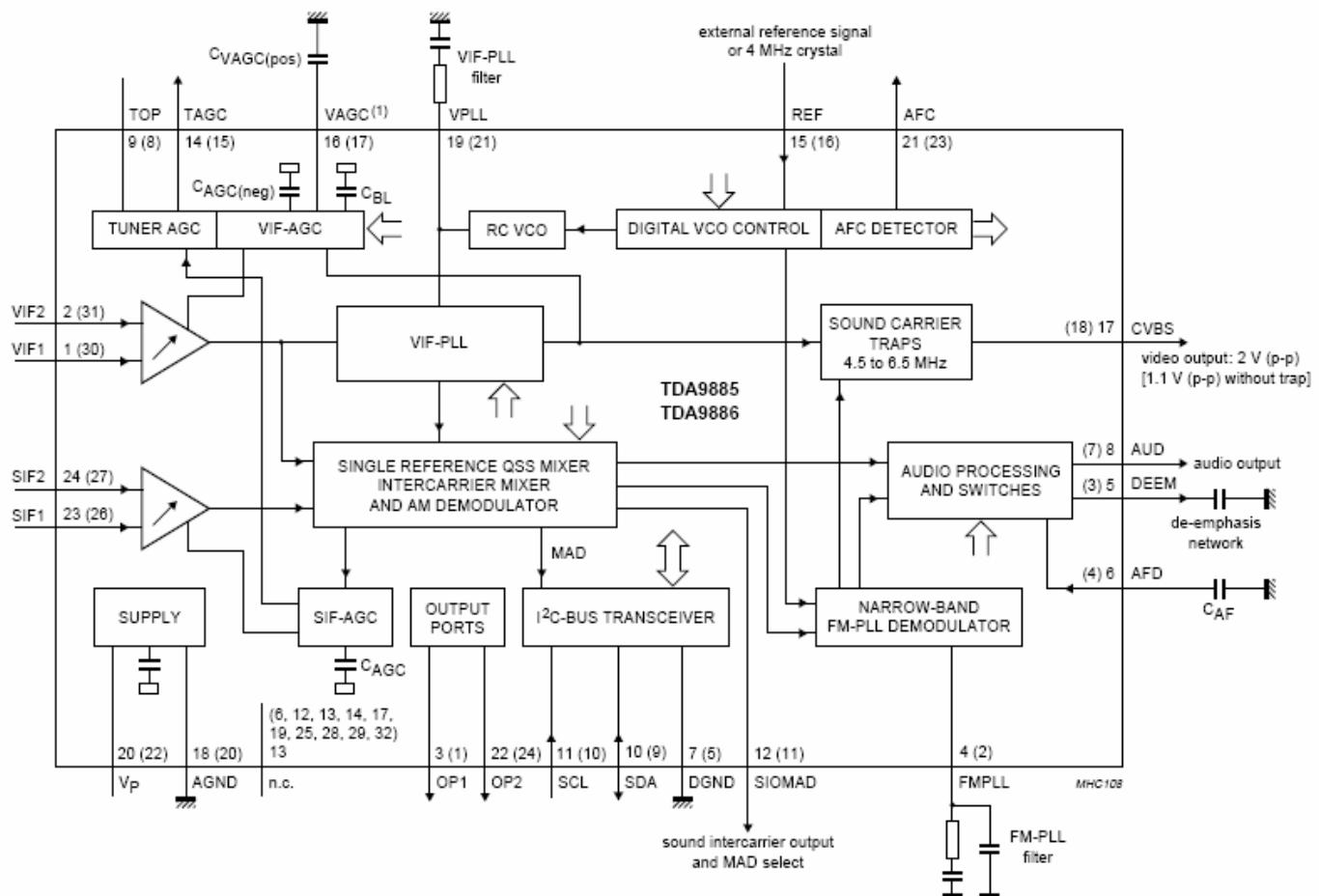

| 6   | U9       | TDA9886T                            | Multistandard alignment-free IF-PLL demodulators                                                                                                                                                                                                                                    |

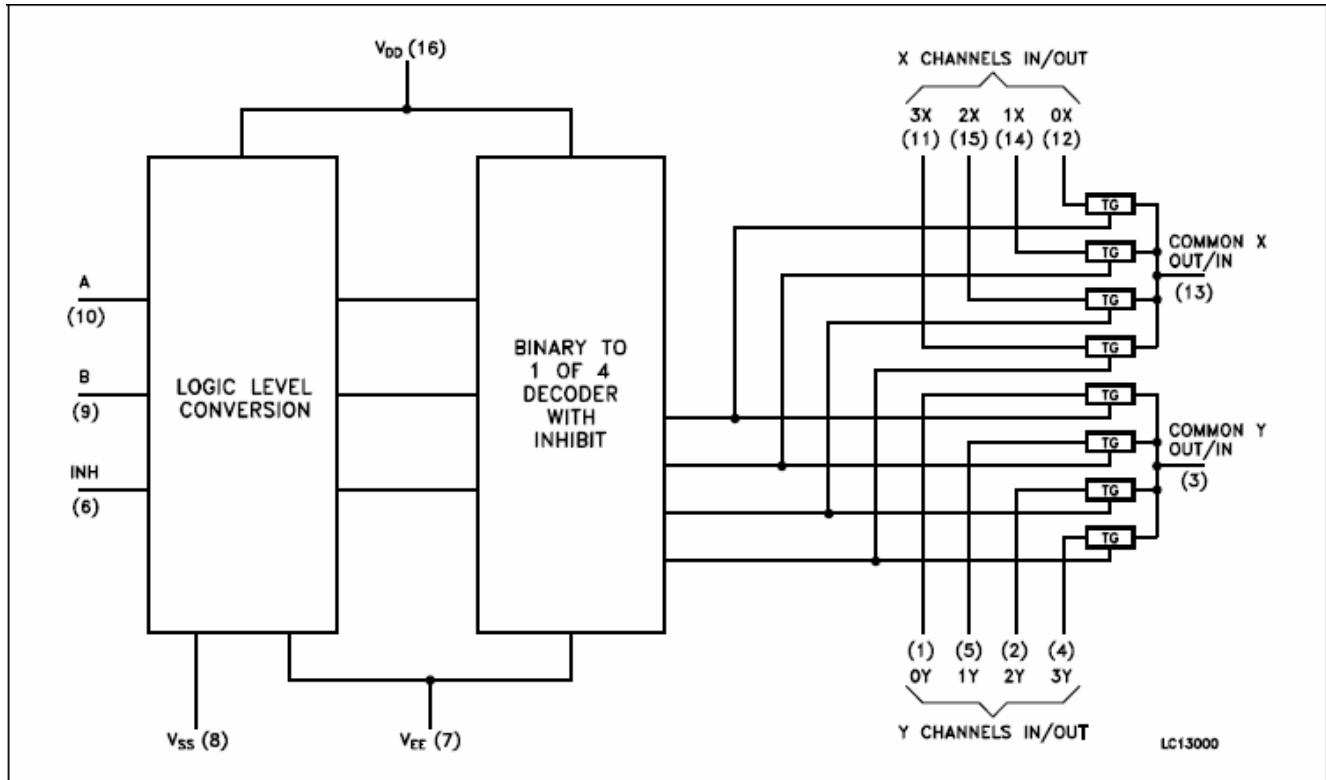

| 7   | U11      | 74HC4052                            | Audio signal switch of AV terminal                                                                                                                                                                                                                                                  |

| 8   | U15      | 74LVC14A                            | VGA line and field synchronizing signal waveform shaping                                                                                                                                                                                                                            |

| 9   | U16      | AT24C64                             | EEPROM                                                                                                                                                                                                                                                                              |

| 10  | U17      | IRF7404/AO4459                      | Field Effect Transistor                                                                                                                                                                                                                                                             |

| 11  | U22      | MP1411DH                            | DC-DC converter                                                                                                                                                                                                                                                                     |

| 12  | U20、U24  | AP1117E33                           | LDO, 5V to 3.3V DC converter                                                                                                                                                                                                                                                        |

| 13  | U23      | AP1122EL                            | LDO, 5V to 1.2V DC converter                                                                                                                                                                                                                                                        |

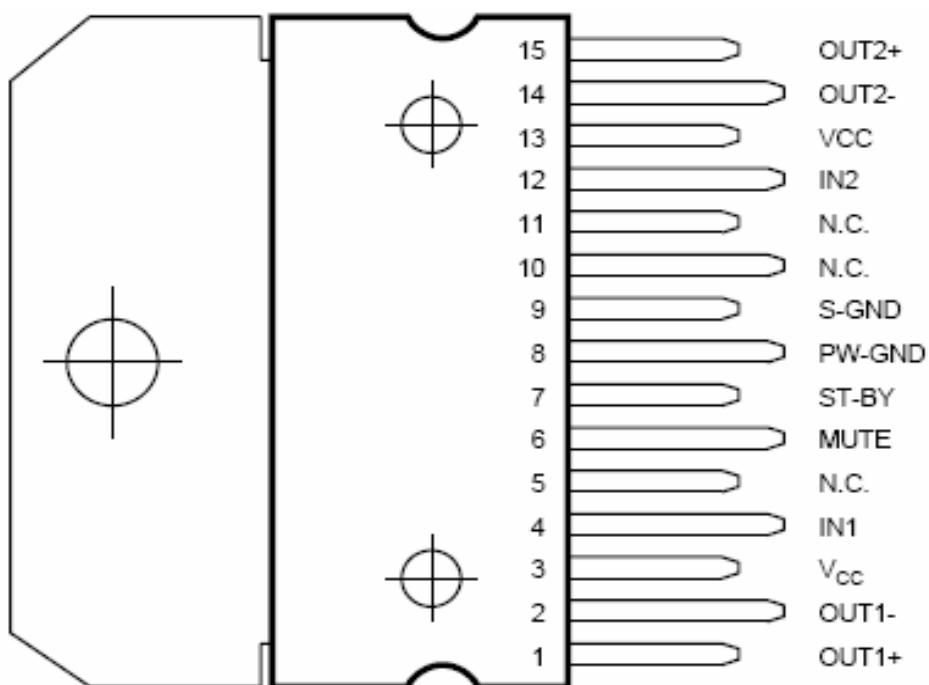

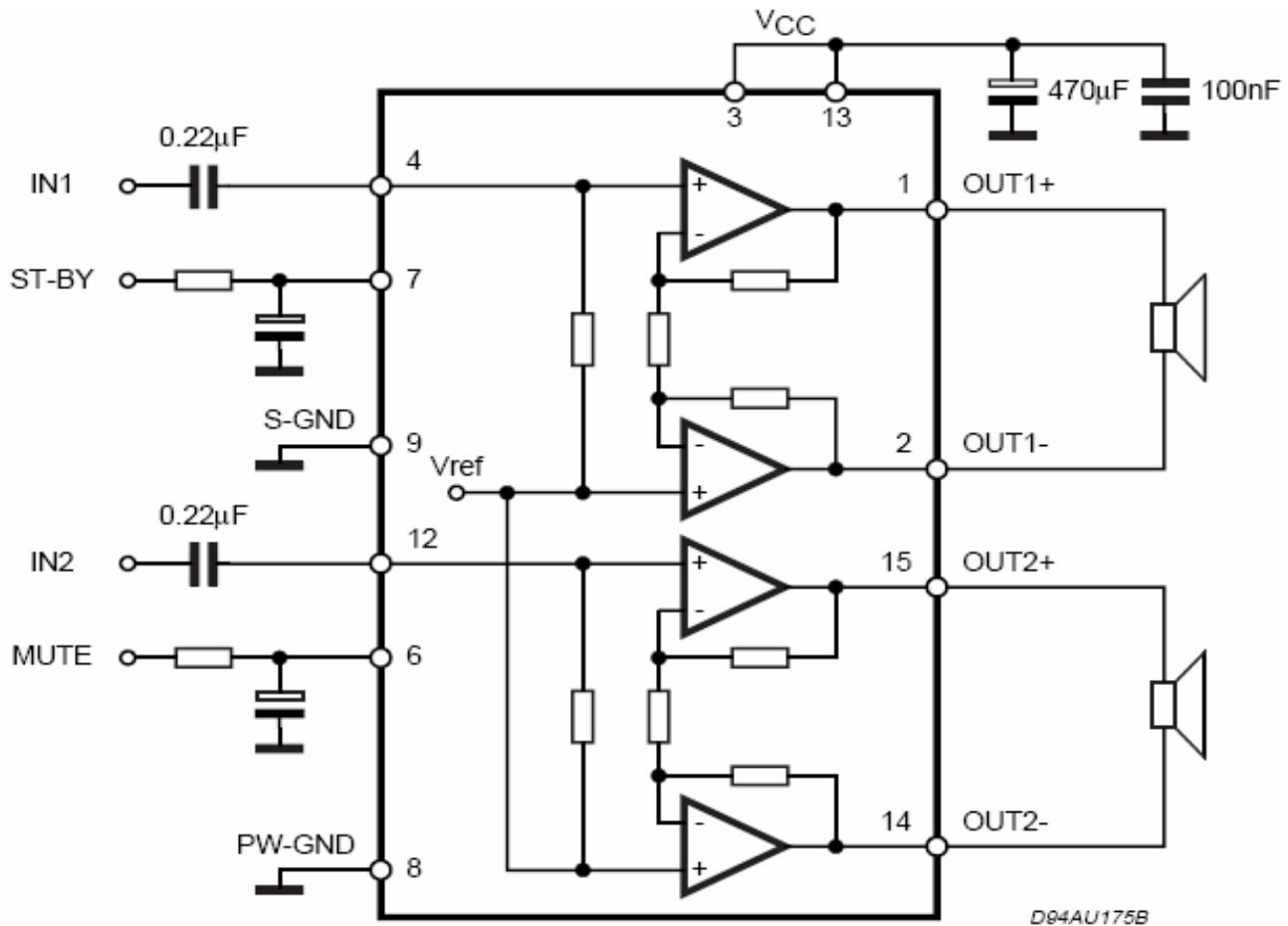

| 14  | U27      | TDA7266SA                           | Audio amplifier (BTL output)                                                                                                                                                                                                                                                        |

| 15  | U32      | PS201                               | HDMI two-to-one switch                                                                                                                                                                                                                                                              |

### 2. Function introduction of ICs or functional module of LCD TV with LS02/PS02 chassis

1. Tuner (Asian TV: AFT7/W003; European TV: AFT7/W103; American TV: AFT7/W300)

| No. | Terminal name | Description            |

|-----|---------------|------------------------|

| 1   | AGC           | AGC voltage supply     |

| 2   | NC            | No Connected           |

| 3   | SAS           | Address Selection Line |

| 4   | SCL           | Serial Clock Line      |

| 5   | SDA           | Serial Data Line       |

| 6   | NC            | No Connected           |

|    |        |                         |

|----|--------|-------------------------|

| 7  | BP     | +B For PLL & Mixer      |

| 8  | ADC/NC | ADC Input/ No Connected |

| 9  | NC     | No Connected            |

| 10 | NC     | No Connected            |

| 11 | IF1    | IF Output               |

| 12 | ANT    | VHF/UHF Signal Input    |

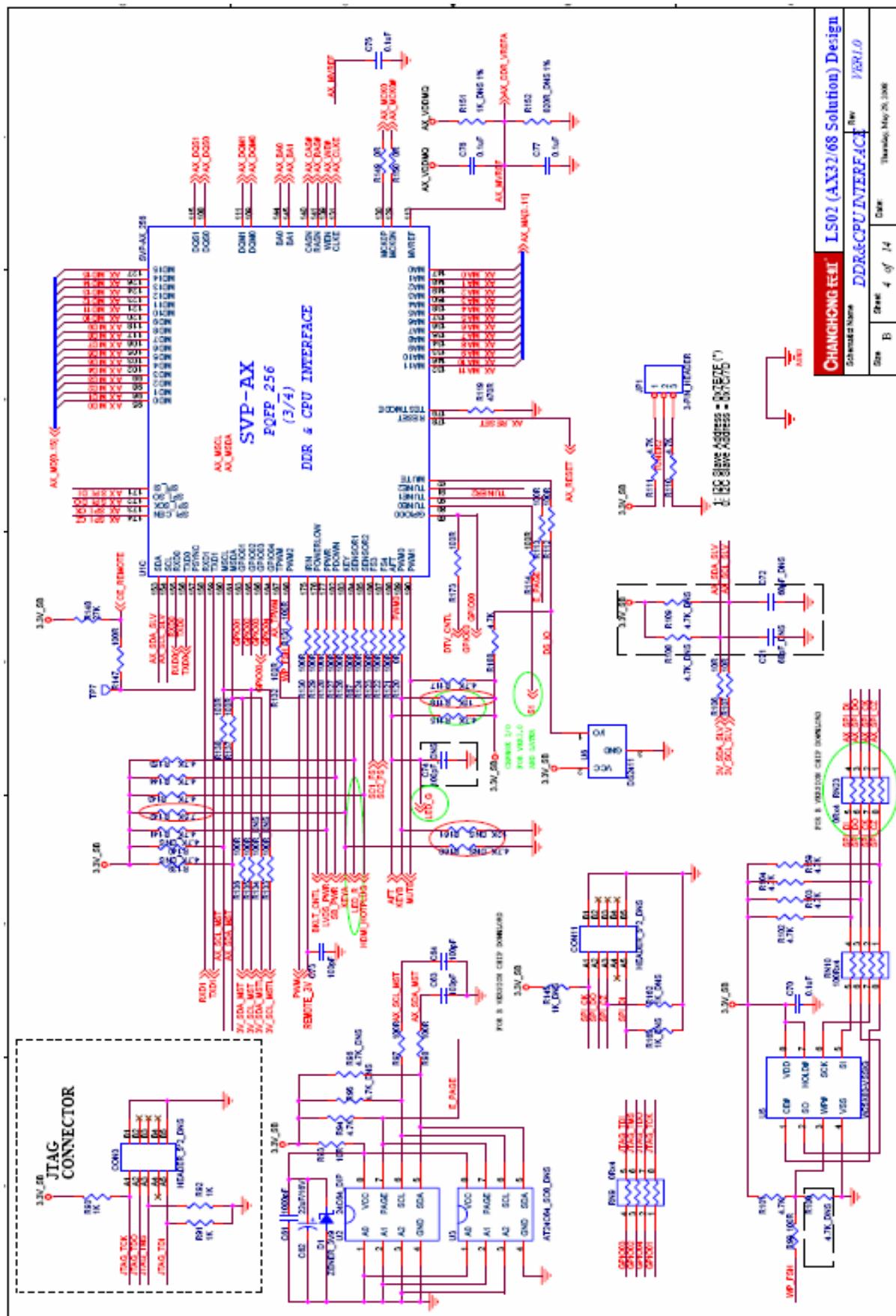

## 2. Video processing IC SVP-AX32LF/SVP-AX68LF

The SVP<sup>TM</sup>CX video processor is a highly integrated system-on-a-chip device, targeting the converging HDTV-ready and PC-ready LCD TV, PDP TV applications where high precision processing of video and data are the requirements. SVPTMCX contains 6th generation dual-purposed triple 10-bit high-precision and high speed video ADCs for both PC and video inputs, the high-performance multi-format 3D digital comb video decoder that supports NTSC, PAL, and SECAM\*, a HDTV sync separator, motion adaptive de-interlacing engine, and the video format conversion engine, supporting multi-window display in many different output modes. Trident's DCRe<sup>TM</sup> – Digital Cinema Reality engine, is integrated inside the SVPTMCX family to provide the most natural cinema-realistic images. The DCRe<sup>TM</sup> technology integrates advanced 3D-comb video decoding, advanced motion adaptive de-interlacing, object-based digital noise reduction, advanced 7th generation scaler, film mode support, average picture level (APL), edge smoothing and dynamic sharpness enhancement. Trident's patented Unified Memory Architecture (UMA) that allows frame rate conversion, 3D comb video decoding, and video enhancement processing to share the same memory buffer that is made up of high-speed and cost-effective PC graphic memory. All these advanced digital processing techniques combined with a true 10-bit video data processing for the most optimal video fidelity to provide the most natural and cinema quality video images. Designed for maximum system design flexibility, SVPTMCX integrates all video interfaces to support converging digital video, analog video, and PC data applications. The users of Trident's single chip SVP<sup>TM</sup>CX series video processor(s) will benefit from many features while maintaining a price competitive advantage over the existing solution(s)

### Main features:

- Integrated 7th Generation Motion and Edge Adaptive De-interlacing

- Integrated ADC

- PC auto tune

- Built-in 8-bit LVDS Transmitter

- Advanced 7th generation cubic-4 image scaling engine

- Advanced Chroma Processing and Dynamic Contrast Function

- Green color stretch, blue color stretch, skin color enhancement

- Integrated 7th Generation Motion Adaptive 3D Digital Comb Video Decoder with Programmable Filter

- 60Hz~100Hz interlaced scanning and 50Hz~75Hz progressive scanning

- frame rate conversion

- 14D: dynamic picture enhancements

- Advanced Film Mode Recovery-3:2/2:2 pull down

- Build-in A/D conversion function

- Teletext function

- Supports 16bits DDR memory interface

- Multi-screen display mode

- OSD and VBI/Closed caption and advanced OSD engine

**Pin function description:**

Table1: Pin Assignments for CPU-related and GPIO pins

| Name    | Type | Pin No. | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                        | Power Supply    |

|---------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| SCL     | I    | 154     | I2C slave SCL, serial clock;                                                                                                                                                                                                                                                                                                                                                                                                           | VDDC/<br>VDDH   |

| SDA     | I/O  | 153     | Shared I2C slave SDA serial data:<br>o SVP video engine I2C slave<br>o embedded 8051CPU peripheral I2C slave<br><b>Bootstrap pin “TUNE2” is used for I2C slave device ID:</b><br>SVP video engine I2C slave:<br>o if pull-up, I2C device ID is 0x7E/7F;<br>o if pull-down, I2C device ID is 0x7C/7D;<br>Embedded 8051CPU peripheral I2C slave:<br>o if pull-up, I2C device ID is 0x6A/6B;<br>o if pull-down, I2C device ID is 0x62/63; | VDDC/<br>VDDH   |

| SPI_SI  | O    | 171     | Serial data output to SI pin of SPI flash memory                                                                                                                                                                                                                                                                                                                                                                                       | VSB12/<br>VSB33 |

| SPI_SO  | I    | 172     | Serial data input from SO pin of SPI flash memory                                                                                                                                                                                                                                                                                                                                                                                      | VSB12/<br>VSB33 |

| SPI_SCK | O    | 173     | Serial clock to SCK pin of SPI flash memory                                                                                                                                                                                                                                                                                                                                                                                            | VSB12/<br>VSB33 |

| SPI_CEN | O    | 174     | Chip enable (active low) to CE# pin of SPI flash memory                                                                                                                                                                                                                                                                                                                                                                                | VSB12/<br>VSB33 |

| RXD0    | I/O  | 155     | o UART0 RXD<br>o Port P30                                                                                                                                                                                                                                                                                                                                                                                                              | VDDC/<br>VDDH   |

| TXD0    | I/O  | 156     | o UART0 TXD                                                                                                                                                                                                                                                                                                                                                                                                                            | VDDC/           |

| Name     | Type | Pin No. | Pin Description                                                                                                                                                                                                                                                                                           | Power Supply    |

|----------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|          |      |         | <ul style="list-style-type: none"> <li>○ Port P31</li> </ul>                                                                                                                                                                                                                                              | VDDH            |

| IRIN     | I/O  | 175     | <ul style="list-style-type: none"> <li>○ InfraRed input</li> <li>○ Port P32</li> <li>○ Interrupt IE0#</li> </ul>                                                                                                                                                                                          | VSB12/<br>VSB33 |

| POWERLOW | I/O  | 176     | <ul style="list-style-type: none"> <li>○ Power voltage down detection monitor input</li> <li>○ Port P33</li> <li>○ Interrupt IE1#</li> </ul>                                                                                                                                                              | VSB12/<br>VSB33 |

| PSYNC    | I/O  | 157     | <ul style="list-style-type: none"> <li>○ Port P34</li> <li>HSYNC output from display engine;</li> <li>VSYNC output from display engine;</li> <li>DE output from display engine;</li> <li>DSS1_VSYNC output;</li> <li>DSS1_HSYNC output;</li> </ul>                                                        | VDDC/<br>VDDH   |

| PWM2     | I/O  | 168     | <ul style="list-style-type: none"> <li>○ PWM2</li> <li>○ port P35</li> <li>HSYNC output from display engine;</li> <li>VSYNC output from display engine;</li> <li>DSS1_VSYNC output;</li> <li>DSS1_HSYNC output;</li> <li>FIELD output from display engine;</li> <li>HDMI MUTE from HDMI audio;</li> </ul> | VDDC/<br>VDDH   |

| PPWR     | I/O  | 177     | <ul style="list-style-type: none"> <li>○ Panel power on sequence control</li> <li>○ Port P36*</li> </ul>                                                                                                                                                                                                  | VSB12/<br>VSB33 |

| PDOWN    | I/O  | 182     | <ul style="list-style-type: none"> <li>○ Power switch control output</li> <li>○ Port P37*</li> <li>○ Input as external trigger of timer 2</li> </ul>                                                                                                                                                      | VSB12/<br>VSB33 |

| RXD1     | I/O  | 158     | <ul style="list-style-type: none"> <li>○ UART1 RXD</li> <li>○ Port P20</li> </ul>                                                                                                                                                                                                                         | VDDC/<br>VDDH   |

| TXD1     | I/O  | 159     | <ul style="list-style-type: none"> <li>○ UART1 TXD</li> <li>○ Port P21</li> </ul>                                                                                                                                                                                                                         | VDDC/<br>VDDH   |

|       |                       |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

|-------|-----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| MSCL  | I/O                   | 160 | <ul style="list-style-type: none"> <li>○ I2C master (software ) SCL</li> <li>○ Port P22;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VDDC/<br>VDDH |

| MSDA  | I/O                   | 161 | <ul style="list-style-type: none"> <li>○ I2C master (software) SDA</li> <li>○ Port P23</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDC/<br>VDDH |

| TUNE0 | I/O                   | 89  | <ul style="list-style-type: none"> <li>○ Tune0</li> <li>○ Port P24</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VDDC/<br>VDDH |

| TUNE1 | I/O                   | 90  | <ul style="list-style-type: none"> <li>○ Tune1</li> <li>○ Port P25</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VDDC/<br>VDDH |

| TUNE2 | O<br>(output<br>only) | 91  | <ul style="list-style-type: none"> <li>○ <b>Bootstrap pin for I2C slave device ID</b><br/>SVP video engine I2C slave: <ul style="list-style-type: none"> <li>○ if pull-up, I2C device ID is 0x7E/7F;</li> <li>○ if pull-down, I2C device ID is 0x7C/7D;</li> </ul> </li> <li>○ <b>Embedded 8051CPU peripheral I2C slave:</b> <ul style="list-style-type: none"> <li>○ if pull-up, I2C device ID is 0x6A/6B;</li> <li>○ if pull-down, I2C device ID is 0x62/63;</li> </ul> </li> <li>○ <b>Tune2</b></li> <li>○ <b>Port P26(output only)</b></li> <li>HSYNC output from display engine;</li> <li>VSYNC output from display engine;</li> <li>DSS1_VSYNC output;</li> <li>DSS1_HSYNC output;</li> </ul> | VDDC/<br>VDDH |

| Name    | Type    | Pin No. | Pin Description                                                                                                                                                                                                                                                                                   | Power Supply    |

|---------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|         |         |         | FIELD output from display engine;<br>DE output from display engine;<br>HDMI MUTE from HDMI audio;                                                                                                                                                                                                 |                 |

| MUTE    | I/O     | 92      | <ul style="list-style-type: none"> <li>○ Mute output for audio control,</li> <li>○ Port P27</li> </ul>                                                                                                                                                                                            | VDDC/<br>VDDH   |

| KEY     | I/O; AI | 183     | <ul style="list-style-type: none"> <li>○ Analog Key input, low speed ADC input AN0</li> <li>○ Port P10</li> </ul>                                                                                                                                                                                 | VSB12/<br>VSB33 |

| SENSOR1 | I/O; AI | 184     | <ul style="list-style-type: none"> <li>○ Analog power sensor, low speed ADC input AN1;</li> <li>○ Port P11</li> </ul>                                                                                                                                                                             | VSB12/<br>VSB33 |

| SENSOR2 | I/O; AI | 185     | <ul style="list-style-type: none"> <li>○ Environment light sensor, low speed ADC input AN2</li> <li>○ Port P12</li> </ul>                                                                                                                                                                         | VSB12/<br>VSB33 |

| FS3     | I/O; AI | 186     | <ul style="list-style-type: none"> <li>○ Function select3, low speed ADC input AN3</li> <li>○ Port P13</li> </ul>                                                                                                                                                                                 | VSB12/<br>VSB33 |

| FS4     | I/O; AI | 187     | <ul style="list-style-type: none"> <li>○ Function select4, low speed ADC input AN4</li> <li>○ Port P14</li> </ul>                                                                                                                                                                                 | VSB12/<br>VSB33 |

| AFT     | I/O; AI | 188     | <ul style="list-style-type: none"> <li>○ Tuner AFC, low speed ADC input AN5</li> <li>○ Port P15</li> <li>○ Interrupt IE2#</li> </ul>                                                                                                                                                              | VSB12/<br>VSB33 |

| PWM0    | I/O; AI | 189     | <ul style="list-style-type: none"> <li>○ PWM0</li> <li>○ Port P16</li> <li>○ Interrupt IE3#</li> <li>○ low speed ADC input AN6</li> </ul>                                                                                                                                                         | VSB12/<br>VSB33 |

| PWM1    | I/O; AI | 190     | <ul style="list-style-type: none"> <li>○ PWM1</li> <li>○ Port P17</li> <li>○ Interrupt IE4#</li> <li>○ low speed ADC input AN7</li> </ul>                                                                                                                                                         | VSB12/<br>VSB33 |

| GPIO00  | I/O     | 88      | <ul style="list-style-type: none"> <li>○ Port P00</li> <li>○ Interrupt IE5#</li> <li>○ Input / output for I2S AUD_SCK optionally</li> </ul>                                                                                                                                                       | VDDC/<br>VDDH   |

| GPIO01  | I/O     | 163     | <ul style="list-style-type: none"> <li>○ JTAG_TCK to SVP-AX (power on default as input)</li> <li>○ Port P01</li> <li>○ I2S input / output master Clock</li> <li>○ SPDIF master clock input / output</li> </ul>                                                                                    | VDDC/<br>VDDH   |

| GPIO02  | I/O     | 165     | <ul style="list-style-type: none"> <li>○ JTAG_TMS to SVP-AX, (power on default as input);</li> <li>○ Port P02</li> <li>○ I2S input / output SCK;</li> </ul>                                                                                                                                       | VDDC/<br>VDDH   |

| GPIO03  | I/O     | 166     | <ul style="list-style-type: none"> <li>○ JTAG_TDI to SVP-AX, power on default as input;</li> <li>○ Port P03</li> <li>○ I2S input / output SD</li> <li>○ SPDIF data input / output</li> </ul>                                                                                                      | VDDC/<br>VDDH   |

| GPIO04  | I/O     | 164     | <ul style="list-style-type: none"> <li>○ JTAG_TDO from SVP-AX, (power on default as output)</li> <li>○ Port P04</li> <li>○ I2S input / output WS</li> </ul>                                                                                                                                       | VDDC/<br>VDDH   |

| TPWM    | I/O     | 167     | Tuning pulse width modulator. High resolution (18 bit) PWM / PFM output, used for VST (voltage synthesis tuning) application, such as panel backlight control; <ul style="list-style-type: none"> <li>○ HSYNC output from display engine;</li> <li>○ VSYNC output from display engine;</li> </ul> | VDDC/<br>VDDH   |

Table2 Pin Assignments for Analog Support Interface

| Name  | Type | Pin No. | Pin Description                                                                              | Power supply                |

|-------|------|---------|----------------------------------------------------------------------------------------------|-----------------------------|

| XTALI | AI   | 194     | Input for Clock Synthesizer. Supports 24.576 MHz Oscillator or crystal powered by analog PLL | PAVDD1 and VSB12 (left bar) |

| XTALO | AI/O | 195     | Used in conjunction with XTALI for 24.576 MHz crystal output powered by analog PLL           | PAVDD1 and VSB12 (left bar) |

| MLF1  | AI   | 197     | Low pass filter node for memory clock PLL powered by analog PLL                              | PAVDD1 and VSB12 (left bar) |

| PLF2  | AI   | 200     | Low pass filter node for video clock PLL powered by analog PLL                               | PAVDD2 and VSB12 (left bar) |

Table3 Pin Assignments for Analog Input Interface

| Name      | Type | Pin No. | Pin Description                             |

|-----------|------|---------|---------------------------------------------|

| CVBS      | AI   | 52      | Composite video input                       |

| Y_G1      | AI   | 33      | Y input 1 of component or G input 1 of RGB  |

| Y_G2      | AI   | 36      | Y input 2 of Component or G input 2 of RGB  |

| Y_G3      | AI   | 42      | Y input 3 of component or G input 3 of RGB  |

| CVBS_OUT1 | AO   | 61      | CVBS Output 1                               |

| CVBS_OUT2 | AO   | 60      | CVBS Output 2                               |

| C         | AI   | 45      | C input of S-Video                          |

| PB_B1     | AI   | 34      | PB Input 1 of component or B input 1 of RGB |

| PB_B2     | AI   | 37      | PB Input 2 of component or B input 2 of RGB |

| PB_B3     | AI   | 43      | PB Input 3 of component or B input 3 of RGB |

| PR_R1     | AI   | 35      | PR Input 1 of component or R input 1 of RGB |

| PR_R2     | AI   | 38      | PR Input 2 of component or R input 2 of RGB |

| PR_R3     | AI   | 44      | PR Input 3 of component or R input 3 of RGB |

| FS1       | AI   | 55      | SCART Function select1                      |

| FS2       | AI   | 54      | SCART Function select2                      |

| FB1       | AI   | 57      | SCART FB input for Port 1                   |

| FB2       | AI   | 56      | SCART FB input for Port 2                   |

| PC_G      | AI   | 29      | Analog input for PC: G                      |

| PC_B      | AI   | 28      | Analog input for PC: B                      |

| PC_R      | AI   | 30      | Analog input for PC: R                      |

| AIN_HS    | I    | 26      | Hsync Input (PC RGB Input)                  |

| AIN_VS    | I    | 27      | Vsync Input (PC RGB Input)                  |

Table4 Pin Assignments for Capture Interface (TV&RGB)

| Name     | Type | Pin No.                                                                        | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                          | Power Supply  |

|----------|------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| DP[15:0] | I/O  | 234, 235, 236, 237, 238, 239, 240, 241, 247, 248, 249, 250, 251, 252, 253, 254 | Digital Input port [15:0], used as 16-bit CCIR601 digital input<br>Digital input port [15:6], used as 10/8-bit CCIR656 digital input<br><br>DP[6]: XRAM address mapped (SVP_GPIO3, input and output)<br>DP[5]: XRAM address mapped (SVP_GPIO2, output only)<br>DP[4]: XRAM address mapped (SVP_GPIO1, output only)<br>HSYNC output from display engine;<br>VSYNC output from display engine;<br>DP[3]: XRAM address mapped (SVP_GPIO4, input and output) | VDDC/<br>VDDH |

| Name   | Type | Pin No. | Pin Description                                                                                                                                                                                                                                | Power Supply  |

|--------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|        |      |         | HSYNC output from display engine;<br>VSYNC output from display engine;<br>DP[1]:<br>HSYNC output from display engine;<br>VSYNC output from display engine;<br>DP[0]:<br>HSYNC output from display engine;<br>VSYNC output from display engine; |               |

| DP_CLK | I/O  | 242     | o Digital port CLK input<br>o Pixel clock output                                                                                                                                                                                               | VDDC/<br>VDDH |

| DP_VS  | I/O  | 256     | o Vsync Input of Digital Port<br>o VSYNC output from display engine<br>o DSS1_VSYNC output                                                                                                                                                     | VDDC/<br>VDDH |

| DP_HS  | I/O  | 255     | o Hsync Input of Digital Port<br>o HSYNC output from display engine<br>o DSS1_HSYNC output                                                                                                                                                     | VDDC/<br>VDDH |

Table5 Pin Assignments for Frame Buffer Memory

| Name     | Type | Pin No.                                                                                         | Pin Description         | Power supply |

|----------|------|-------------------------------------------------------------------------------------------------|-------------------------|--------------|

| MD[15~0] | I/O  | 127, 126,<br>124, 123,<br>121, 120,<br>118, 117,<br>106, 105,<br>103, 102,<br>99, 98, 96,<br>95 | Memory Data             | VDDC/VDDM    |

| MA[11~0] | I/O  | 132, 146,<br>133, 134,<br>135, 136,<br>137, 138,<br>150, 149,<br>148, 147                       | Memory Address          | VDDC/VDDM    |

| RASN     | O    | 141                                                                                             | RAS#                    | VDDC/VDDM    |

| CASN     | O    | 140                                                                                             | CAS#                    | VDDC/VDDM    |

| WEN      | O    | 139                                                                                             | WE#, write enable       | VDDC/VDDM    |

| MCK0P    | O    | 130                                                                                             | Memory Clock +          | VDDC/VDDM    |

| MCK0N    | O    | 129                                                                                             | Memory Clock -          | VDDC/VDDM    |

| DQM[1~0] | O    | 111, 109                                                                                        | Read/write bytes enable | VDDC/VDDM    |

| CLKE     | O    | 131                                                                                             | Memory Clock Enable     | VDDC/VDDM    |

| DQS[1~0] | IO   | 115                                                                                             | Memory Data Strobe      | VDDC/VDDM    |

| MVREF    | PWR  | 108                                                                                             | DDR Voltage Reference   | VDDC/VDDM    |

| BA0      | O    | 144                                                                                             | Bank Address Select     | VDDC/VDDM    |

| BA1      | O    | 145                                                                                             | Bank Address Select     | VDDC/VDDM    |

Table6 Miscellaneous Pin Assignments

| Name     | Type | Pin No. | Pin Description                                                                         | Power Supply |

|----------|------|---------|-----------------------------------------------------------------------------------------|--------------|

| RESET    | I    | 178     | System reset active high, with Schmitt Trigger. RESET forces the chip to a known state. | VSB12/VSB33  |

| TESTMODE | I    | 179     | Reserved (Connected to GND)                                                             | VSB12/VSB33  |

Table7 LVDS Output Pin Assignments

| Name   | Type | Pin No. | Pin Description                                             |

|--------|------|---------|-------------------------------------------------------------|

| TA1P   | AO   | 226     | LVDS 1 <sup>st</sup> channel Differential positive data out |

| TA1M   | AO   | 227     | LVDS 1 <sup>st</sup> channel Differential negative data out |

| TB1P   | AO   | 224     | LVDS 1 <sup>st</sup> channel Differential positive data out |

| TB1M   | AO   | 225     | LVDS 1 <sup>st</sup> channel Differential negative data out |

| TC1P   | AO   | 222     | LVDS 1 <sup>st</sup> channel Differential positive data out |

| TC1M   | AO   | 223     | LVDS 1 <sup>st</sup> channel Differential negative data out |

| TD1P   | AO   | 218     | LVDS 1 <sup>st</sup> channel Differential positive data out |

| TD1M   | AO   | 219     | LVDS 1 <sup>st</sup> channel Differential negative data out |

| TCLK1P | AO   | 220     | LVDS 1 <sup>st</sup> channel Differential positive CLK out  |

| TCLK1M | AO   | 221     | LVDS 1 <sup>st</sup> channel Differential negative CLK out  |

| TA2P   | AO   | 212     | LVDS 2 <sup>nd</sup> channel Differential positive data out |

| TA2M   | AO   | 213     | LVDS 2 <sup>nd</sup> channel Differential negative data out |

| TB2P   | AO   | 210     | LVDS 2 <sup>nd</sup> channel Differential positive data out |

| TB2M   | AO   | 211     | LVDS 2 <sup>nd</sup> channel Differential negative data out |

| TC2P   | AO   | 208     | LVDS 2 <sup>nd</sup> channel Differential positive data out |

| TC2M   | AO   | 209     | LVDS 2 <sup>nd</sup> channel Differential negative data out |

| TD2P   | AO   | 204     | LVDS 2 <sup>nd</sup> channel Differential positive data out |

| TD2M   | AO   | 205     | LVDS 2 <sup>nd</sup> channel Differential negative data out |

| TCLK2P | AO   | 206     | LVDS 2 <sup>nd</sup> channel Differential positive CLK out  |

| TCLK2M | AO   | 207     | LVDS 2 <sup>nd</sup> channel Differential negative CLK out  |

Table8 HDMI Interface Pin Assignments

| Name         | Type | Pin No.      | Pin Description                             |

|--------------|------|--------------|---------------------------------------------|

| PVCC         | PWR  | 2            | TMDS PLL Supply Voltage                     |

| AVCC         | PWR  | 3, 7, 11, 15 | TMDS Analog Supply Voltage                  |

| RXC-         | AO   | 4            | HDMI Differential CLK-                      |

| RXC+         | AO   | 5            | HDMI Differential CLK+                      |

| TMDS_GND     | PWR  | 1            | TMDS GND                                    |

| RX0-         | AI   | 8            | HDMI Differential Input Pair 0-             |

| RX0+         | AI   | 9            | HDMI Differential Input Pair 0+             |

| RX1-         | AI   | 12           | HDMI Differential Input Pair 1-             |

| RX1+         | AI   | 13           | HDMI Differential Input Pair 1+             |

| RX2-         | AI   | 16           | HDMI Differential Input Pair 2-             |

| RX2+         | AI   | 17           | HDMI Differential Input Pair 2+             |

| AVDD33_Audio | PWR  | 25           | ACR PLL Regulator Supply Voltage            |

| AVSS33_Audio | GND  | 24           | ACR PLL GND                                 |

| PWR5V        | I    | 21           | TMDS Port Transmitter Detect (5V tolerance) |

| DSCL         | I    | 19           | DDC I2C Clock for DDC (5V Tolerance)        |

| DSDA         | I/O  | 20           | DDC I2C Data for DDC (5V tolerance)         |

Table9 Analog Audio Input/Output Interface Pin Assignments

| Name      | Type | Pin No. | Pin Description                                                                                                                  |

|-----------|------|---------|----------------------------------------------------------------------------------------------------------------------------------|

| SIFP      | AI   | 50      | SIF Audio Input                                                                                                                  |

| SIFN      | AI   | 51      | Reference ground for SIF audio input                                                                                             |

| AL1       | AI   | 73      | Audio line input left channel 1                                                                                                  |

| AR1       | AI   | 74      | Audio line input right channel 1                                                                                                 |

| AL2       | AI   | 75      | Audio line input left channel 2                                                                                                  |

| AR2       | AI   | 76      | Audio line input right channel 2                                                                                                 |

| AL3       | AI   | 77      | Audio line input left channel 3                                                                                                  |

| AR3       | AI   | 78      | Audio line input right channel 3                                                                                                 |

| AL4       | AI   | 79      | Audio line input left channel 4                                                                                                  |

| AR4       | AI   | 80      | Audio line input right channel 4                                                                                                 |

| AOL1      | AO   | 81      | SCART Audio Output left channel 1                                                                                                |

| AOR1      | AO   | 82      | SCART Audio Output right channel 1                                                                                               |

| HPHOL     | AO   | 63      | <ul style="list-style-type: none"> <li>○ Headphone output left channel</li> <li>○ SCART audio output left channel 2</li> </ul>   |

| HPHOR     | AO   | 64      | <ul style="list-style-type: none"> <li>○ Headphone output right channel</li> <li>○ SCART audio output right channel 2</li> </ul> |

| SPKOL     | AO   | 66      | Main Audio/Speaker output left channel                                                                                           |

| SPKOR     | AO   | 67      | Main Audio/Speaker output right channel                                                                                          |

| VREFP     | AI   | 71      | Input Analog reference voltage positive. Intended for 3.3V                                                                       |

| VREFN     | AI   | 69      | Input Analog reference voltage negative. Intended for system analog ground.                                                      |

| VCM       | AO   | 70      | Output Analog common-mode voltage                                                                                                |

| VCC33A    | PWR  | 72      | Power for main analog, 3.3V                                                                                                      |

| GND33A    | GND  | 68      | Ground for main analog                                                                                                           |

| VCC33A_HP | PWR  | 62      | Power for head phone amplifier, 3.3V                                                                                             |

| GND33A_HP | GND  | 65      | Ground for head phone amplifier, 3.3V                                                                                            |

Table10 Digital Audio Interface Pin Assignments

| Name     | Type | Pin No. | Pin Description                                                                                                                                                                              | Power supply |

|----------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| AUD_MCLK | I/O  | 85      | <ul style="list-style-type: none"> <li>○ I2S audio input/output master clock</li> <li>○ SPDIF master clock input / output</li> <li>○ XRAM address mapped (SVP_GPIO3, output only)</li> </ul> | VDDC / VDDH  |

| AUD_SD   | I/O  | 86      | <ul style="list-style-type: none"> <li>○ I2S audio input/output data</li> <li>○ SPDIF data input/output</li> <li>○ XRAM address mapped (SVP_GPIO2, input/output)</li> </ul>                  | VDDC / VDDH  |

| AUD_WS   | I/O  | 87      | <ul style="list-style-type: none"> <li>○ I2S audio input/output word select</li> <li>○ XRAM address mapped (SVP_GPIO1, input/output)</li> </ul>                                              | VDDC / VDDH  |

Table11 Pin Assignments for Power and Ground

| Name                 | Type | Pin No. | Pin Description                           |

|----------------------|------|---------|-------------------------------------------|

| VSB12 (top bar)      | PWR  | 192     | 1.2V, Standby power for core              |

| VSB12_PLL (left bar) | PWR  | 193     | 1.2V, Standby power for KMNPLL 1.2v       |

| VSB33                | PWR  | 180     | 3.3V, Standby power for I/O               |

| PAVDD1               | PWR  | 198     | Standby Power for analog PLL MCLK (3.3 V) |

| Name                         | Type | Pin No.                                       | Pin Description                           |

|------------------------------|------|-----------------------------------------------|-------------------------------------------|

| PAVSS1                       | GND  | 196                                           | Ground for analog PLL                     |

| PAVSS2                       | GND  | 199                                           | Ground for analog PLL                     |

| PAVDD2                       | PWR  | 201                                           | Standby Power for analog PLL PCLK (3.3 V) |

| VDDC                         | PWR  | 23, 83, 100,<br>122, 151,<br>169, 233,<br>244 | 1.2V Digital Core Power                   |

| VDDH                         | PWR  | 93, 162,<br>246                               | 3.3V Digital I/O Power                    |

| VSSR                         | GND  | 112                                           | Digital Ground                            |

| VDDR                         | PWR  | 114                                           | Digital Power for Memory                  |

| VDDM                         | PWR  | 116                                           | DDR memory Interface Power                |

| AVSS3_BG_ASS                 | GND  | 58                                            | ADC Ground                                |

| AVDD3_BG_ASS                 | PWR  | 59                                            | ADC Power                                 |

| PAVDD1, 2                    | PWR  | 198, 201                                      | Power for ANAPLL/APLL/LLPLL, 1.2V         |

| PAVSS1, 2                    | GND  | 196, 199                                      | Ground for ANAPLL/APLL/LLPLL              |

| AVDD_ADC4, 3, 2, 1           | PWR  | 47, 32, 40,<br>49                             | Power for analog ADC (1.2 V)              |

| AVSS_ADC1 and<br>AVSS_ADC234 | GND  | 48, 31, 39,<br>46                             | Ground for analog ADC1 and ADC234         |

| AVDD3_ADC1, 2                |      | 53, 41                                        | Power for analog ADC (3.3 V)              |

| LVDS_VDDO                    | PWR  | 202, 217,<br>228                              | LVDS Output Buffer VDD, 3.3 V             |

| LVDS_VSSO                    | GND  | 203, 214,<br>229                              | LVDS Output Buffer GND                    |

| LVDS_VDDP                    | PWR  | 216                                           | LVDS PLL VDD, 1.2 V                       |

| LVDS_VSSP                    | GND  | 215                                           | LVDS PLL GND                              |

SVP-CX32LF/ SVP-CX68LF internal block diagram:

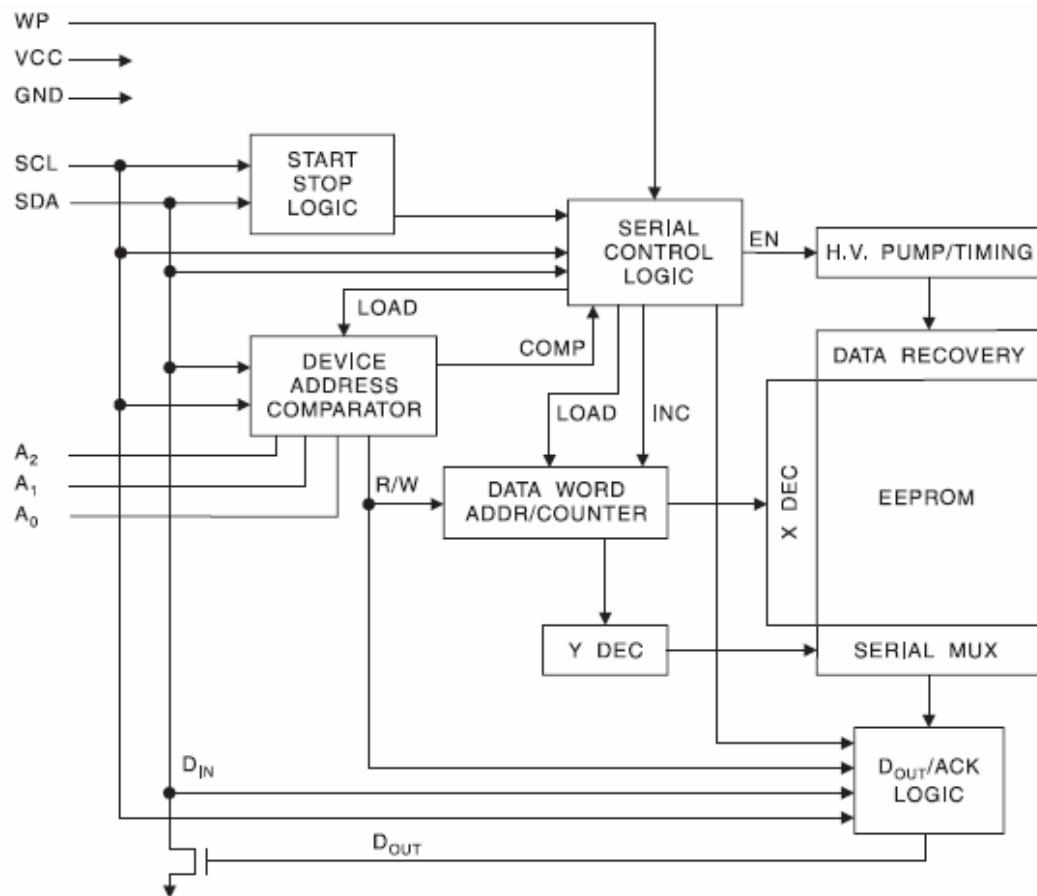

### 3. AT24C64-SO8-DNS brief introduction:

The AT24C64A provides 65,536 bits of serial electrically erasable and programmable read only memory (EEPROM) organized as 8192 words of 8 bits each. The device's cascadable feature allows up to 8 devices to share a common two-wire bus. The device is optimized for use in many industrial and commercial applications where low power and low voltage operation are essential. The AT24C64A is available in space saving 8-lead JEDEC PDIP, 8-lead JEDEC SOIC, 8-lead EIAJ SOIC, 8-lead MAP and 8-lead TSSOP packages and is accessed via a 2-wire serial interface. In addition, the entire family is available in 2.7V (2.7V to 5.5V) and 1.8V (1.8V to 5.5V) versions.

Main features:

- Low-Voltage and Standard-Voltage Operation

- 2.7 (VCC = 2.7V to 5.5V)

- 1.8 (VCC = 1.8V to 5.5V)

- Low-Power Devices (ISB = 6 $\mu$ A @ 5.5V) Available

- Internally Organized 4096 x 8, 8192 x 8

- Two-wire Serial Interface

- Schmitt Trigger, Filtered Inputs for Noise Suppression

- Bidirectional Data Transfer Protocol

- 100 kHz (1.8V) and 400 kHz (2.5V) Clock Rate for AT24C32A

- 400 kHz (1.8V) Clock Rate for AT24C64A

- Write Protect Pin for Hardware Data Protection

- 32-byte Page Write Mode (Partial Page Writes Allowed)

- Self-timed Write Cycle (5 ms Max)

- High Reliability

- Endurance: 1 Million Write Cycles

- Data Retention: 100 Years

- Automotive Grade, Extended Temperature and Lead-free/Halogen-free Devices Available

- 8-lead JEDEC PDIP, 8-lead JEDEC SOIC, 8-lead EIAJ SOIC, 8-lead MAP and 8-lead TSSOP Packages

- Die Sales: Wafer Form, Waffle Pack, and Bumped Wafers

Pin Configuration

| Pin NO. | Pin Name | Function           |

|---------|----------|--------------------|

| 1-3     | A0 – A2  | Address Inputs     |

| 4       | GND      | Ground             |

| 5       | SDA      | Serial Data        |

| 6       | SCL      | Serial Clock Input |

| 7       | WP       | Write Protect      |

| 8       | VCC      | Power Supply       |

AT24C64-SO8-DNS internal functional block diagram:

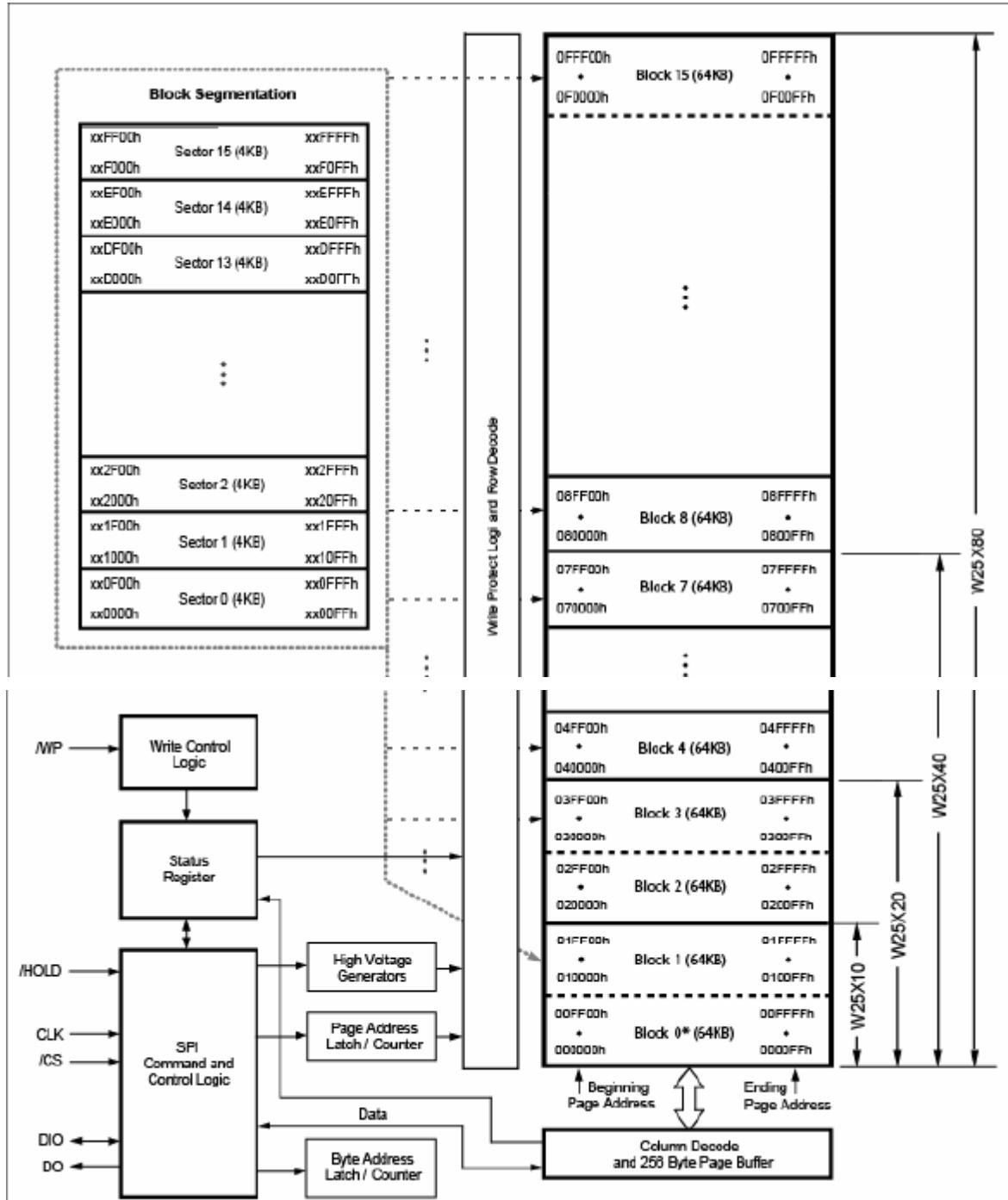

#### 4. W25X80-VSSIG brief introduction

W25X80-VSSIG main features:

■ Family of Serial Flash Memories

- 8M-bit/1M-byte(1,048,576)

- 256-bytes per programmable page

- Uniform 4K-byte Sectors/64K-byte Blocks

■ SPI with Single or Dual Outputs

- Clock, Chip Select, Data I/O, Data Out

- Optional Hold function for SPI flexibility

■ Data Transfer up to 150M-bits/second

- Clock operation to 75MHz

- Fast Read Dual Out instruction

- Auto-increment Read capability

■ Flexible Architecture with 4KB sectors

- Sector Erase(4K-bytes)

- Block Erase(64K-byte)

- Page program up to 256 bytes<2ms

■ Low Power Consumption, Wide Temperature Range

- Single 2.7 to 3.6V supply

- 5mA active current, 1uA Power-down (typ)

■ Software and Hardware Write Protection

- Write-Protect all or portion of memory

- Enable/Disable protection with /WP pin

- Top or bottom array protection

Pin introduction:

| Pin NO. | Pin Name | I/O | Function            |

|---------|----------|-----|---------------------|

| 1       | /CS      | I   | Chip Select Input   |

| 2       | DO       | O   | Data Output         |

| 3       | /WP      | I   | White Protect input |

| 4       | GND      |     | Ground              |

| 5       | DIO      | I/O | Data Input/Output   |

| 6       | CLK      | I   | Serial Clock Input  |

| 7       | /HOLD    | I   | Hold input          |

| 8       | VCC      |     | Power Supply        |

W25X80-VSSIG internal block diagram:

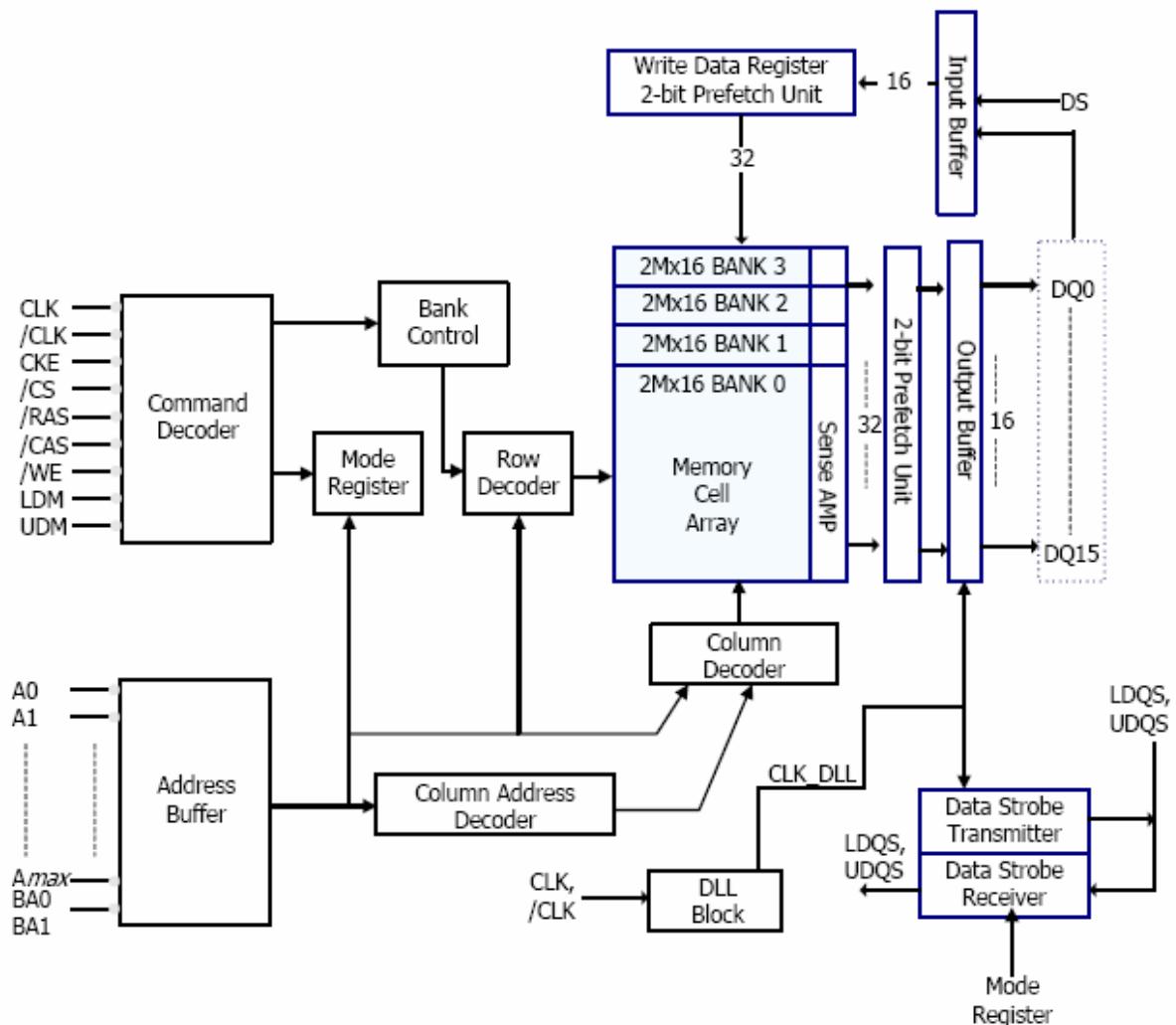

##### 5. HY5DU281622FTP-4 brief introduction:

The HY5DU281622FT(P) is a 134,217,728-bit CMOS Double Data Rate(DDR) Synchronous DRAM, ideally suited for the main memory applications which requires large memory density and high bandwidth. This Hynix 128Mb DDR SDRAMs offer fully synchronous operations referenced to both rising and falling edges of the clock. While all addresses and control inputs are latched on the rising edges of the CK (falling edges of the /CK), Data, Data strobes and Write data masks inputs are sampled on both rising and falling edges of it.

The data paths are internally pipelined and 2-bit prefetched to achieve very high bandwidth. All input and output voltage levels are compatible with SSTL\_2.

main features:

- VDD, VDDQ = 2.3V min ~ 2.7V max

(Typical 2.5V Operation +/- 0.2V for DDR266, 333)

- VDD, VDDQ = 2.4V min ~ 2.7V max

(Typical 2.6V Operation +0.1/- 0.2V for DDR400, 400Mbps/pin product and 500Mbps/pin product )

- All inputs and outputs are compatible with SSTL\_2 interface

- Fully differential clock inputs (CK, /CK) operation

- Double data rate interface

- Source synchronous - data transaction aligned to bidirectional data strobe (DQS)

- x16 device has two bytewide data strobes (UDQS,LDQS) per each x8 I/O

- Data outputs on DQS edges when read (edged DQ)

- Data inputs on DQS centers when write (centered DQ)

- On chip DLL align DQ and DQS transition with CK transition

- DM mask write data-in at the both rising and falling edges of the data strobe

- All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock

- Programmable CAS latency 2/2.5 (DDR266, 333) and 3/4 (DDR400, 400Mbps/pin product and 500Mbps/pin product) supported

- Programmable burst length 2/4/8 with both sequential and interleave mode

- Internal four bank operations with single pulsed/RAS

- Auto refresh and self refresh supported

- tRAS lock out function supported

- 4096 refresh cycles/64ms

- JEDEC standard 400mil 66pin TSOP-II with 0.65mm pin pitch

- Lead free (\*ROHS Compliant)

Pin introduction:

| PIN                       | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, /CK                   | Input  | Clock: CK and /CK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of /CK. Output (read) data is referenced to the crossings of CK and /CK (both directions of crossing).                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CKE                       | Input  | Clock Enable: CKE HIGH activates, and CKE LOW deactivates internal clock signals, and device input buffers and output drivers. Taking CKE LOW provides PRECHARGE POWER DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWER DOWN (row ACTIVE in any bank). CKE is synchronous for POWER DOWN entry and exit, and for SELF REFRESH entry. CKE is asynchronous for SELF REFRESH exit, and for output disable. CKE must be maintained high throughout READ and WRITE accesses. Input buffers, excluding CK, /CK and CKE are disabled during POWER DOWN. Input buffers, excluding CKE are disabled during SELF REFRESH. CKE is an SSTL_2 input, but will detect an LVCMOS LOW level after <i>VDD</i> is applied. |

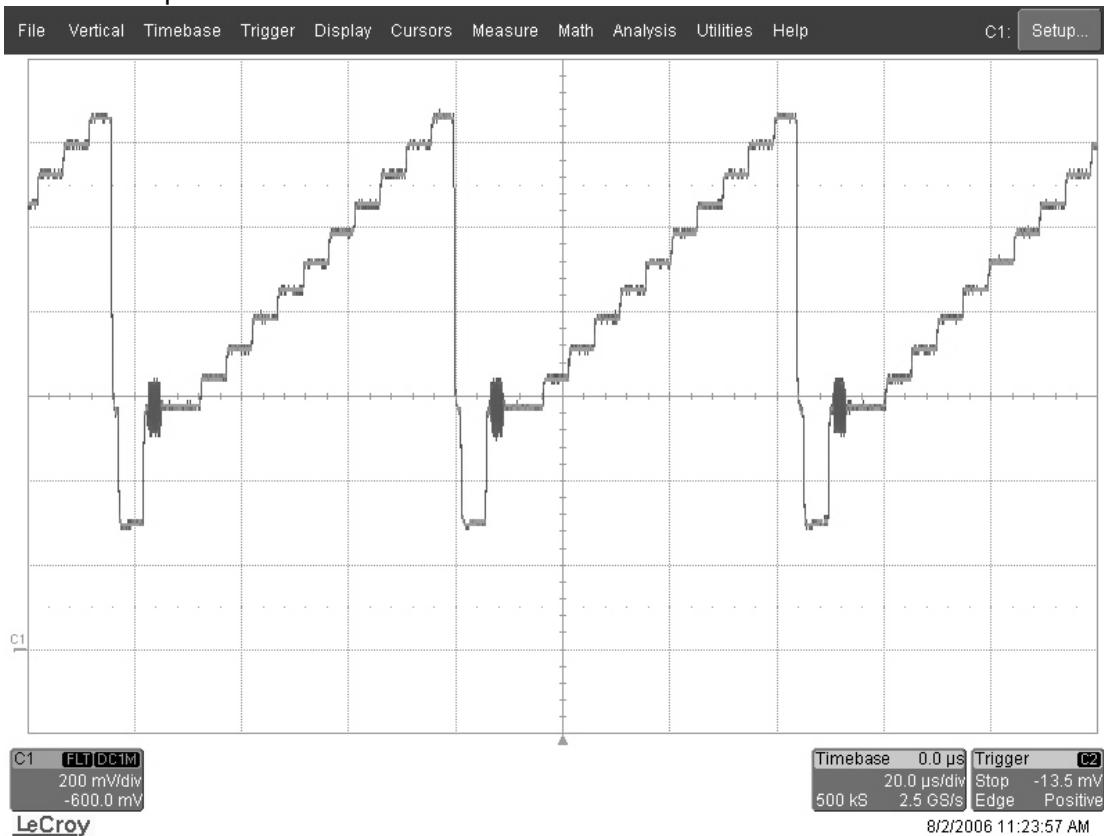

| /CS                       | Input  | Chip Select: Enables or disables all inputs except CK, /CK, CKE, DQS and DM. All commands are masked when Chip Select is registered high. Chip Select provides for external bank selection on systems with multiple banks. Chip Select is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BA0, BA1                  | Input  | Bank Address Inputs: BA0 and BA1 define to which bank an ACTIVE, Read, Write or PRECHARGE command is being applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A0 ~ A11                  | Input  | Address Inputs: Provide the row address for ACTIVE commands, and the column address and AUTO PRECHARGE bit for READ/WRITE commands, to select one location out of the memory array in the respective bank. A10 is sampled during a precharge command to determine whether the PRECHARGE applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1. The address inputs also provide the op code during a MODE REGISTER SET command. BA0 and BA1 define which mode register is loaded during the MODE REGISTER SET command (MRS or EMRS).                                                                                                               |

| /RAS, /CAS, /WE           | Input  | Command Inputs: /RAS, /CAS and /WE (along with /CS) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |