Unit in mm

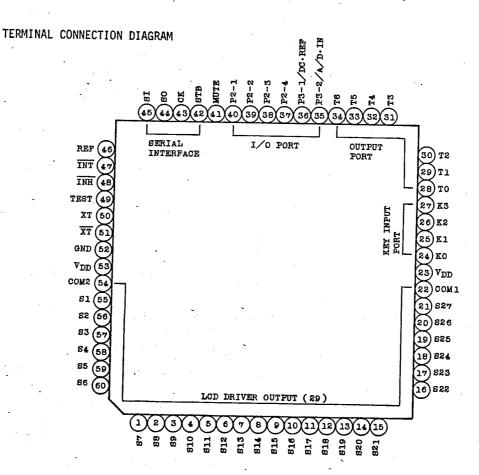

The TC9306F is 4 bit CMOS micro controller for digital tuning system use having built-in LCD driver.

CPU has 4 bit parallel addition and subtraction (AI, SI instructions, etc.), logical operation (OR, AN instructions, etc.), plural bit judge and comparison instruction (TM, SL instructions, etc.), and timer function.

The equipment consists of 60 pin, mini-flat package, and has abundant I/O port and exclusive key input port controlled by powerful input and output instruction (IO, KEY instruction, etc.), and serial bus control function (SIO instruction) to control forcibly external PLL LSI and peripheral ICs. Further, it contains 4 bit A/D converter, and is capable of measuring electric field strength by inputting signal meter output.

Also, it has abundant exclusive LCD output terminal of 172 duty, 1/2 bias driving, and exclusive terminal to output ten kinds of reference frequency signal to be supplied to PLL LSI.

And TC9306F is pin-compatible with TC9302AF (program memory capacity, 1K-step type).

#### (v<sub>DD</sub>) (v<sub>DD</sub>) 14.0±0.1 17.6±03 1.8±0.3 MARK naanaanaanaa X C35 | Q8 57 7 JEDEC TOSHIBA F60BA2-P

Weight : 0.85g

#### FEATURES:

- . 4 bit micro controller for digital tuning system use.

- . Built-in LCD driver (1/2 duty, 1/2 bias driving, driving frequency: 50Hz)

- .  $5V\pm10\%$  single power supply. CMOS structure and low power dissipation.

- . Back-up of data memory (RAM) and each port is easily made (by  $\overline{\text{INH}}$  terminal).

- Program memroy (ROM) : 16 bit × 2048 steps

- . Data memory (RAM) : 4 bit ×256 words

- . Powerful instruction set of 65 kinds (all one word instruction).

- . Instruction executing time  $44.4\mu s$  (7.2MHz crystal connection).

T-49-19-57

Abundant addition and subtraction instructions (addition instructions 12 kinds, subtraction instructions 12 kinds).

- . Powerful compound judge statement (TMTR,TMFR,TMT,TMF,TMIN,TMFN instructions).

- . Data transfer in same low address is possible.

- . Indirect transfer of register is possible. (MVRD, MVRS, MVGD, MVGS instructions).

- . 16 powerful general registers (arranged in RAM).

- . Stack level: 2 level

- . Program memory (ROM) has no conception of page, field, and JUMP and CAL instruction can be freely made among 2048 steps.

- . It is possible to freely refer to the content, 16 bits, of optional address within 1024 steps in program memory (ROM), (DAL instruction).

- . Contains powerful exclusive serial bus control function.

- . Powerful input and output instruction (IO, KEY, SIO instructions).

- . Exclusive input port  $(K_0 \sim K_3)$  for key input use, and abundant 29 exclusive LCD driving terminals.

- Abundant 14 I/O port (port capable of setting input or output in 1 bit unit : 6, exclusive output port : 8).

- . Clock stop is possible by instruction. (During CKSTP instruction : Supply current,  $1\mu A$  or below).

- . 2Hz timer F/F and 10Hz interval pulse output are contained (Internal port for time base use).

- . Built-in 4 bit A/D converter

- Reference frequencies of ten kinds to be supplies to PLL LSI can be selected depending upon program. (1kHz, 5kHz, 9kHz, 10kHz, 12.5kHz, 25kHz, 50kHz, 100kHz, 3.125kHz, 6.25kHz).

- . Pin-compatible with TC9302AF (ROM capacity: 16-bit ×1024 steps).

MAXIMUM RATINGS (Ta=25°C)

| CHARACTERISTIC        | SYMBOL      | RATING                    | UNIT |

|-----------------------|-------------|---------------------------|------|

| Supply Voltage        | $v_{ m DD}$ | -0.3~6.0                  | v    |

| Input Voltage         | VIN         | -0.3~V <sub>DD</sub> +0.3 | v    |

| Power Dissipation     | PD          | 200                       | mW   |

| Operating Temperature | Topr        | -30~75                    | °c   |

| Storage Temperature   | Tstg        | -55~125                   | °C   |

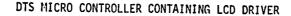

TOP VIEW MINI FP-60PIN

TOSHIRA

-- 006-

T-49-19-57

AUDIO DIGITAL IC

MUTE

O K3 O K3 O K3

La

INT V<sub>DD</sub>

POWER ON

GND

RESET

INH La

ĪNH

SYSTEM RESET

TEST

$n \mid \underline{n}$

STACK REG.

III STACK REG.

T-49-19-57

| ELECTRICAL CHARACTERISTICS | (Unless otherwise specified,    | m 058a           |

|----------------------------|---------------------------------|------------------|

| <del></del>                | variable offict wise shecilled. | Ta=25"(: Vnn=5V) |

| (01.1                             |                   | rwise specified, Ta=                                | 25*                                    | $^{\prime}$ C, $^{\prime}$ V $_{ m I}$       | D=5V)       |                                        |              |        |

|-----------------------------------|-------------------|-----------------------------------------------------|----------------------------------------|----------------------------------------------|-------------|----------------------------------------|--------------|--------|

| CHARACTERISTIC                    | SYMBO             | DL TEST CONDITION                                   | _                                      | MIN                                          | I. TY       | P. MA                                  | X. UNI       | -      |

| Supply Voltage Range              | $v_{\mathrm{DD}}$ |                                                     | *                                      | <del> </del>                                 | <del></del> |                                        | <del> </del> |        |

| Memory Holding Voltage Range      | $v_{HD}$          | Crystal oscillation stops                           | *                                      |                                              |             | 5.                                     | <del></del>  |        |

| Operating Supply Current          | I <sub>DD</sub>   | Normal operation<br>(Encluding output<br>current)   |                                        | -                                            | 1.0         | 3.                                     | O mA         |        |

| Memory Holding Supply Current     | I <sub>HD1</sub>  | V <sub>DD</sub> =5V<br>Crystal oscillation<br>stops |                                        | _                                            | 0.07        | 1.0                                    | 0            |        |

|                                   | I <sub>HD2</sub>  | V <sub>DD</sub> ≈2V<br>Crystal oscillation<br>stops |                                        | -                                            | -           | 0.5                                    | - μA<br>5    | V V AA |

| Crystal Oscillation Frequency     | f <sub>XT</sub>   |                                                     | *                                      |                                              | 7.2         | <del>  _</del>                         | MHz          | -      |

| LCD Common Output (COM1, COM2)    |                   |                                                     |                                        |                                              | 1           | ــــــــــــــــــــــــــــــــــــــ | 1 11112      | _      |

| High Level Output Current         | IOH1              | V <sub>OH</sub> =4.5V                               | T                                      | -200                                         | -500        | T                                      | T            | 7      |

| Low Level Output Current          | I <sub>OL1</sub>  | V <sub>OL</sub> =0.5V                               | +                                      | 200                                          | 500         | <del> </del>                           | μΑ           | 1      |

| 1/2 Bias Voltage                  | VBS               | `                                                   | +                                      | 2.40                                         | 2.50        | 2.60                                   | μΑ           |        |

| LCD Segment Output (S1~S27)       |                   | <u> </u>                                            | _!_                                    | 2.40                                         | 12.50       | 2.00                                   | <u>v</u>     | J      |

| High Level Output Current         | I <sub>OH2</sub>  | V <sub>OH</sub> =4.5V                               | Т                                      | -50                                          | -160        | T                                      | T :          | ı      |

| Low Level Output Current          | I <sub>OL2</sub>  | V <sub>OI.</sub> =0.5V                              | +                                      | 50                                           | 160         | <del>      </del>                      | μΑ           | l      |

| MUTE, T0~T6 Port                  |                   |                                                     | i                                      | - 30                                         | 100         |                                        | μА           |        |

| High Level Output Current         | I <sub>OH3</sub>  | V <sub>OH</sub> =4.5V                               | Τ.                                     | -0.7                                         | -1.7        | Г                                      | <del></del>  | i      |

| Low Level Output Current          | I <sub>OL3</sub>  | V <sub>OL</sub> =0.5V                               | ╬                                      | 0.5                                          |             | <u> </u>                               | mA           |        |

| REF Output, P2-1~-4, P3-1~-2 Port |                   |                                                     | ــــــــــــــــــــــــــــــــــــــ | 0.5                                          | 1.2         | <u> </u>                               | mA           |        |

| High Level Output Current         | I <sub>OH4</sub>  | V <sub>OH</sub> =4.0V                               | 7                                      | 0.6                                          | -1.4        |                                        |              |        |

| ow Level Output Current           |                   | V <sub>OL</sub> =1.0V                               | +                                      | 0.6                                          | 1.4         |                                        | mA           |        |

| O, CK, STB Output                 |                   | -OL 2101                                            |                                        | 0.6                                          | 1.4         |                                        | mA           |        |

| igh Level Output Current          | I <sub>OH5</sub>  | V <sub>OH</sub> =4.0V                               | Τ.                                     | 1.0                                          | 20          |                                        |              |        |

| ow Level Output Current           |                   | V <sub>OL</sub> =1.0V                               | +                                      | 1.0                                          | -2.0        | -                                      | mA           |        |

| ey Input Port (KO~K3)             | 0110              | OF TANK                                             | <u></u>                                | 1.0                                          | 2.0         |                                        | mA           |        |

| igh Level Input Voltage           | v <sub>IH1</sub>  |                                                     | Γ.                                     | <u>,                                    </u> |             |                                        |              |        |

| ow Level Input Voltage            | VILI              |                                                     | -                                      | 3.5                                          | ~           | 5.0                                    | v            |        |

| ulldown Resistance                | R <sub>IN1</sub>  |                                                     | <del> </del>                           | 50                                           | 100         | 1.5                                    | V            |        |

|                                   |                   |                                                     | l                                      | ט כ                                          | TOO         | 150                                    | kΩ           |        |

T-49-19-57

ELECTRICAL CHARACTERISTICS (Unless otherwise specified

| ELLCTRICAL CHARACTERISTICS (UNITE    | s other          | wise specified, 1a=23 | C, VDD | = 3 V )     |      |      |

|--------------------------------------|------------------|-----------------------|--------|-------------|------|------|

| CHARACTERISTIC                       | SYMBOL           | TEST CONDITION        | MIN.   | TYP.        | MAX. | UNIT |

| SI, INH, INT, P2-14, P3-12 Por       | rt               |                       |        |             |      |      |

| High Level Input Voltage (INH)       | VIH2             |                       | 4.3    | *           | 5.0  | V    |

| Low Level Input Voltage (INH)        | V <sub>IL2</sub> |                       | 0      |             | 2.7  | V    |

| High Level Input Voltage (Others)    | v <sub>IH1</sub> |                       | 3.5    |             | 5.0  | V    |

| Low Level Input Voltage (Others)     | VILL             |                       | 0      | *           | 1.5  | V    |

| High Level Input Leak Current        | IIH              | V <sub>IH</sub> =5.0V | -      | -           | 1.0  | μΑ   |

| Low Level Input Leak Current         | IIL              | VIL=0V                | -      | -           | -1.0 | μΑ   |

| A/D Converter (DC·REF, A/D IN)       |                  |                       |        |             |      |      |

| DC·REF Built-in Ladder<br>Resistance | RL               |                       | 30     | 50          | 80   | kΩ   |

| DC.REF Input Voltage Range           | VREF             |                       | 1.0    | ~           | 3.0  | V    |

| Resolution                           | V <sub>RES</sub> |                       | -      | VREF<br>/16 | -    | v    |

| Others                               |                  |                       |        |             |      |      |

| XT Input Feedback Resistance         | Rf               |                       | 500    | 1000        | 2000 | kΩ   |

| Test Input Pulldown Resistance       | RIN2             |                       | 15     | 30          | 60   | kΩ   |

|                                      |                  |                       |        |             |      |      |

Note: \* Marked items are guaranteed within a range of  $VDD=4.5\sim5.5V$ ,  $Ta=-30\sim75^{\circ}C$ .

T-49-19-57

|               | · · · · · · · · · · · · · · · · · · · | EACH TERMINAL            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

|---------------|---------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| PIN<br>No.    | J SVMROT                              | TERMINAL<br>NAME         | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | REMARKS     |

| 22<br>54      | COM1<br>COM2                          | LCD<br>Common Output     | This is a common signal output terminal to LCD Indication of maximum 54 segments is possible with matrix made with S1~S27. To this termina are outputted three value levels of VDD,1/2VDD, GND, at intervals of 50Hz.  (Note) During system reset and CKSTP instruction execution, output is automatically fixed at "L" level.                                                                                                                                                                      | $v_{ m DD}$ |

| 55            | S1<br>₹<br>S6<br>S7<br>₹<br>S27       | LCD<br>Segment<br>Output | This is a segment signal output terminal to LCD. Indication of maximum 54 segments is possible with matrix mode with COM1,COM2.  Data is outputted to these terminals by the execution of SEG instruction (COM1 system) and MARK instruction (COM2 system).  Decoding of segment can be done by making that decode pattern within ROM territory and executing it by using DAL instruction.  (Note) During system reset and CKSTP instruction execution, output is automatically fixed at "L" level. | 0-≪         |

| 24<br>{<br>27 | KO<br>₹ K3                            | Key Input<br>Port        | This is a 4 bit input port for inputting key matrix. By executing KEY instruction designating this port at operand part, data of these terminals is read in RAM.  All terminals contain pull-down resistance.  Usually, output port of T0~T6 is used for key return timing signal output.                                                                                                                                                                                                           | O DO-       |

T-49-19-57

| PIN<br>No.    | SYMBOL                                     | TERMINAL<br>NAME                                                         | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | REMARKS             |

|---------------|--------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 28<br>₹<br>34 | T0                                         | Key Timing<br>Output Port                                                | This is an output port of 4 bit (T0~T3) and 3 bit (T4~T6). Usually, it is used as key return timing signal output of key matrix.                                                                                                                                                                                                                                                                                                                                                                                          | <b>○</b> —≪}        |

| 35            | P3-2<br>/A/D.<br>IN<br>P3-1<br>/DC.<br>REF | I/O Port 3<br>A-D/Analog<br>Voltage Input<br>/Reference<br>Voltage Input | This is a 2 bit I/O port. This port is capable of making input and output assignment for each bit, and the assignment is made with the content of internal port called PORT-3 I/O CONTROL.  This terminal combines analog input of builtin 4 bit A/D Converter. Change-over to A/D Converter input is also controlled by the content of PORT-3 I/O CONTROL Port.  The built-in A/D converter is of successive comparison system by program, P3-1 being reference voltage input, and P3-2 analog comparison voltage input. | To A/D<br>Converter |

| 37<br>≀<br>40 | P2-4<br>₹<br>P2-1                          | I/O Port 2                                                               | This is a 4 bit I/O port. This port is capable of designating input and output of each bit, and the designation is performed with the content of internal port called PORT-2 I/O CONTROL.                                                                                                                                                                                                                                                                                                                                 | L TUO               |

| 41            | MUTE                                       | Muting Signal<br>Output Port                                             | This is a 1 bit output port.  It is usually used as a muting control signal output.                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>○</b> —≪         |

T-49-19-57

| PIN<br>No. | SYMBOL | TERMINAL<br>NAME                                 | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                    | REMARKS                   |

|------------|--------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 42         | STB    | Strobe Pulse<br>Output<br>Serial Clock<br>Output | Serial interface.  By executing SIO instruction, external PLL  LSI and peripheral optional ICs can be                                                                                                                                                                                                                                                     | <b>○</b> —≪}-             |

| 44,        | so     | Serial Data<br>Output                            | As for serial transfer system, two kinds of NCD/NCD mode can be selected by program.                                                                                                                                                                                                                                                                      |                           |

| 45         | SI     | Serial Data<br>Input                             |                                                                                                                                                                                                                                                                                                                                                           | <b>○</b> — <b>&gt;</b> ∞- |

|            |        |                                                  | This is an output terminal of reference frequency signal supplied to PLL LSI.  It is possible to select ten kinds of                                                                                                                                                                                                                                      |                           |

| 46         | REF    | Reference<br>Frequency<br>Signal Output          | reference frequency signal, 1kHz, 5kHz, 9kHz, 10kHz, 12.5kHz, 25kHz, 50kHz, 100kHz, 3.125kHz, 6.25kHz, depending upon the program.                                                                                                                                                                                                                        | <b>○</b> —≪               |

|            |        |                                                  | (Note) When TNH input is at "L" level, output is automatically fixed at "L" level.                                                                                                                                                                                                                                                                        |                           |

| 47         |        | Initializing<br>Input                            | This is a system reset signal input terminal of the device. While INT is at "L" level, reset is applied, and when it becomes "H" level, the program starts from zero address. When the voltage, OV \rightarrow 4.5V, is supplied to VDD terminal, system reset is applied (power on reset), and so this terminal usually is fixed at "H" level when used. | <b>○</b>                  |

|            |        |                                                  | (Note) After system reset, I/O port is set at input mode, but the output port must be initialized by program according to your use, as its output condition is indefinite.                                                                                                                                                                                |                           |

T-49-19-57

| PIN | SYMBOL | TERMINAL                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T       |

|-----|--------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| No. | SIMBUL | NAME                       | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | REMARKS |

| 48  | INH    | Inhibit Input              | This is a pulsing signal input port of radio mode.  It judges as radio on mode at "H" level input and radio off mode at "L" level input.  When this terminal is at "L" level, REF output is automatically fixed at "L" level.  Further, if CKSTP instruction is used in the program and this CKSTP instruction is executed while INH is at "L" level, the internal clock generator and CPU stop their operations, and memory back up condition can be realized at low current consumption (less than 1µA).  At this time, all output terminals (display output, output port, etc.) are fixed to "L" level, automatically. | -       |

|     |        |                            | (Note) CKSTP instruction is effective when INH is at "L" level, and makes the same operation as NOOP instruction if executed when INH is at "H" level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

| 49  | TEST   | Test Mode<br>Control Input | This is an input terminal for a test mode control.  It is brought to test mode with "H" level input and normal operation with "L" level or NC condition. It contains pull down resistance, and usually fixed at NC or "L" level when used.  In the test mode, the device operates as evaluator chip, and program evaluation at EPROM base is possible when combined with external simulation board.                                                                                                                                                                                                                       | O PRINZ |

#### FUNCTIONS OF EACH TERMINAL

| PIN<br>No. | SYMBOL      | TERMINAL<br>NAME                   | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                             | REMARKS |

|------------|-------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 50<br>51   | XT<br>XT    | Crystal<br>Oscillation<br>Terminal | This is a connecting terminal of crystal resonator. 7.2MHz crystal is connected. Oscillation is automatically stopped during the execution of CKSTP instruction.                                                                                                                                                                                                   | -       |

| 52         | GND         | Ground `<br>Terminal               | This is a device ground terminal.                                                                                                                                                                                                                                                                                                                                  | _       |

| 23         | $v_{ m DD}$ | Power Supply<br>Terminal           | This is a power supply terminal of the device. Voltage of $5V\pm10\%$ is impressed in the normal operation.  Under back up condition (during the execution of CKSTP instruction), voltage can be lowered down to $2V$ .  When voltage, $0V\rightarrow4.5V$ , is supplied to this terminal, system reset is applied to the device, and the program starts from zero | · ·     |

|            |             |                                    | address. (power on reset).  (Note) Carry out power on reset from the condition of INH="L" level.  (Note) As the content of each port (output port, internal port, etc.) is indefinite at the time of closing of supply power, initialization by program must be made, according to your use.                                                                       | ·       |

(Supplement)

O Built-in pulldown resistance CMOS input

○—— CMOS output

O Clocked gate type CMOS output