# Contents

| 1.Safety instruction                         | .2  |

|----------------------------------------------|-----|

| 2.Specification                              | .4  |

| 3.Signal processing and system block diagram | 5   |

| 4.Part list                                  | 7   |

| 5.General assembly drawing                   | 10  |

| 6.General connection diagram                 | .11 |

| 7.Failures analysis                          | .15 |

| 8.Description of main ICs and components     | 19  |

# Notice: This service manual is only read and used by professionals. The repairman should review the part of safety precaution before work.

## **1.Safety instruction**

TO PREVENT POSSIBLE DANGER, DAMAGE, AND BODILY HARM, PLEASE CONSIDER AND OBSERVE ALL CAUTIONS CONTAINED IN THIS PARAGRAPH.

### **A.Warning**

If you don't consider the following warning before maintenance, it could result in death or serious injury.

(1) The PDP module is controlled by voltage about 350V. If you need to handle the module during operation or just after power-off, you must take proper precautions against electric shock and never touch the drive circuit portion and metallic part of PDP module.

The capacitors in the drive circuit portion remain temporarily charged even after the power off. After turning off the power, you must be sure to wait at least one minute before touching the module. If the remainder of voltage is strong enough, it could result in electric shock.

- (2) Do not use any other power supply voltage than the specified voltage in this product specifications. If you use deviated power voltage from the specifications, it could result in fire hazard or product failure.

- (3) Do not operate or install under the deviated surrounding from the environmental specification such as in moisture or rain; near water-for example, bath tub, laundry tub, kitchen sink; in a wet basement; or near a swimming pool; and also near fire or heater for example, near or over radiator heat resistor; or where it is exposed to direct sunlight; or somewhere like that. If you use the PDP module in places above, it could result in electric shock, fire hazard or product failure.

- (4) If any foreign objects (e.g. water, liquid and metallic chip or dust) entered the PDP module, the power supply voltage to the PDP module must be turned off immediately. Also never push objects of any kind into the PDP module as they may touch dangerous voltage point or make short circuits that could result in fire hazard or electric shock.

- (5) If smoke, offensive smell or unusual noise should come from the PDP module, the power supply voltage to the PDP module must be turned off immediately. Also, when the PDP screen cannot display any picture after the power-on or during operation, the power supply must be turned off immediately. Never continue to operate the PDP module under these conditions.

- (6) Do not disconnect or connect the PDP module's connector while the power supply is on, or just after power off. Because the PDP module is operated by high voltage, and the capacitors in drive circuit remain temporarily changed even after the power is turned off. If you need to disconnect it, you have to wait at least one minute after power off.

- (7) Do not disconnect or connect the power connector by wet hands. The voltage of the product may be strong enough to cause an electric shock..

- (8) Do not damage the power cable of the PDP module, also do not modify it.

- (9) When the power cable or connector is damaged or frayed, do not use it.

- $(1 \ 0)$  When the power connector is covered with dust, please wipe it with a dry cloth before the power on.

### **B**. Caution

If you don't consider the following cautions, it may result in personal injury or damage to the product.

- (1) Do not set the PDP module on an unstable place, vibrating place or inclined place. The PDP module may fall or drop, and it may cause serious injury to a person, and serious damage to the product.

- (2) If you need to remove the PDP module to another place, you must turn off the power supply and detach the interface cable and power cable from the PDP module, and watch your steps during the work. If the cable has a damage, it may result in fire hazard or electric shock. Also if the PDP module drop or fall, it may result in personal injury.

- (3) When you draw or insert the PDP's cable, you must turn off the power supply and do it with holding the connector. If you draw the cable, the electric wire in the cable could be exposed or broken. It may result in fire hazard or electric shock.

- (4) To carry the PDP module, it be done by two workers in order to avoid unexpected accidents.

- (5) The PDP module has a glass-plate. If the PDP module is inflicted with excessive stress for example; shock, vibration, bending and heat-shock, the glass plate could break. It may result in personal injury. And also, do not press or strike the glass surface.

- (6) If the glass plate was broken, do not touch it with bare hand. It may result in a cut injury.

- (7) Do not place any object on the glass plate. It may scratch or break the glass plate.

- (8) Do not place any object on the PDP module. It may result in personal injury due to its fall or drop.

# 2.Specifications

| Туре                       | PLA-4200M                                                       |

|----------------------------|-----------------------------------------------------------------|

| System of the broadcasting | NTSC-M                                                          |

| System of the video signal | PAL/NTSC/SECAM                                                  |

| Number of stored programs  | 125                                                             |

| Scope of the channel       | Air: CH2 to CH69,<br>Cable: CATV1 to CATV125                    |

| Signal intensity           | 70dB                                                            |

| Audio input                | Input impedance> $10k \Omega$ ,<br>Input voltage 0.1-0.5 V(rms) |

| Speaker output             | 2*5W                                                            |

| Visual angle (Max)         | 160°                                                            |

| Resolution                 | 852*480                                                         |

| Power supply               | AC 100V-240V (50Hz/60Hz)                                        |

| Energy consumption         | 350W(typ).3W (stand by)                                         |

| Dimensions (W*H*D)         | 46.1*29.1*5.2 inch                                              |

| Size of screen             | 42 inch                                                         |

| Aspect ration              | 16:9                                                            |

| Weight                     | 110 lb.                                                         |

| Ambient temperature        | 0-35°C                                                          |

| Ambient humidity           | 20%-70%RH                                                       |

| Ambient air pressure       | 86-106Kpa                                                       |

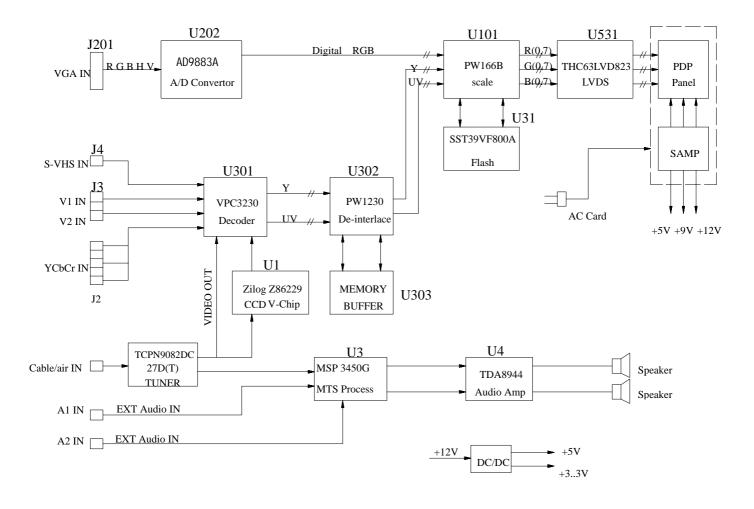

# 3.Signal processing and system block diagram

## A. Image signal processing block diagram

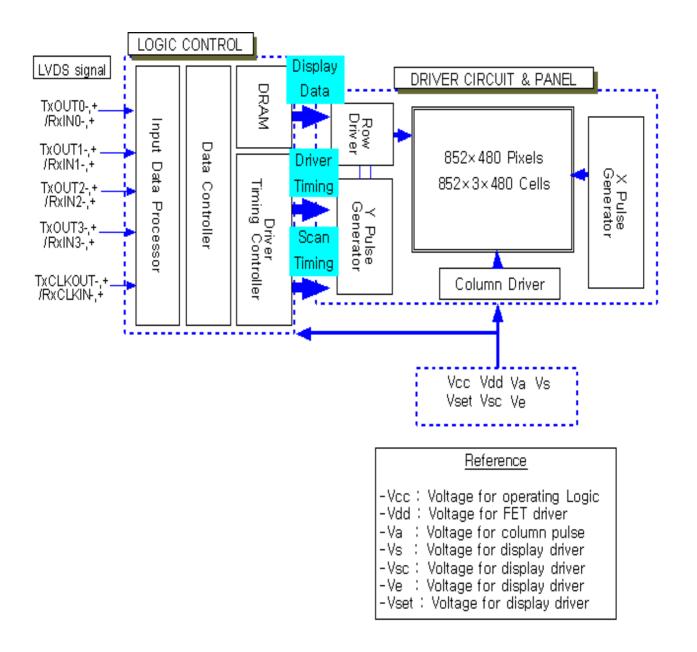

## **B.** PDP DISPLAY SCREEN BLOCK DIAGRAM

# 4.Part list

Part Number

Description

Qty.

| SPW5.069.166 | Polaroid PLA-4200M YPbPr Circuit Board              | 1  |

|--------------|-----------------------------------------------------|----|

| SPW5.969.003 | Polaroid PLA-4200M Remote Control Circuit Board     | 1  |

| A920008      | Polaroid PLA-4200M Zinnia PDP Control Circuit Board | 1  |

| B135011      | Polaroid PLA-4200M 5W-8Ω Speaker                    | 8  |

| SPW8.339.008 | Polaroid PLA-4200M Main Power Button                | 1  |

| E143221JF    | Polaroid PLA-4200M Tapping Screw ST3*8F             | 2  |

| E143222JH    | Polaroid PLA-4200M Tapping Screw ST3*8 (black)      | 6  |

| E143461      | Polaroid PLA-4200M Tapping Screw ST4*16             | 16 |

| E143463      | Polaroid PLA-4200M Tapping Screw ST4*16 (black)     | 6  |

| E144231      | Polaroid PLA-4200M Tapping Screw ST3*10             | 30 |

| E144431      | Polaroid PLA-4200M Tapping Screw ST4*10             | 3  |

| E690220      | Polaroid PLA-4200M SEMS Screw M3*8                  | 16 |

| E690221      | Polaroid PLA-4200M SEMS Screw M3*8 (black)          | 6  |

| E690223      | Polaroid PLA-4200M SEMS Screw M3*8 (black)          | 15 |

| E690230      | Polaroid PLA-4200M SEMS Screw M3*10                 | 2  |

| E690420      | Polaroid PLA-4200M SEMS Screw M4*8                  | 14 |

| E690660      | Polaroid PLA-4200M SEMS Screw M6*16 (black)         | 10 |

| E690670      | Polaroid PLA-4200M SEMS Screw M6*20 (black)         | 4  |

| S070183      | Polaroid PLA-4200M Power Switch KDC-A04-1           | 1  |

| G330170      | Polaroid PLA-4200M Remote Control                   | 1  |

# 4.Part list

This page left intentionally blank.

# 4.Part list

This page left intentionally blank.

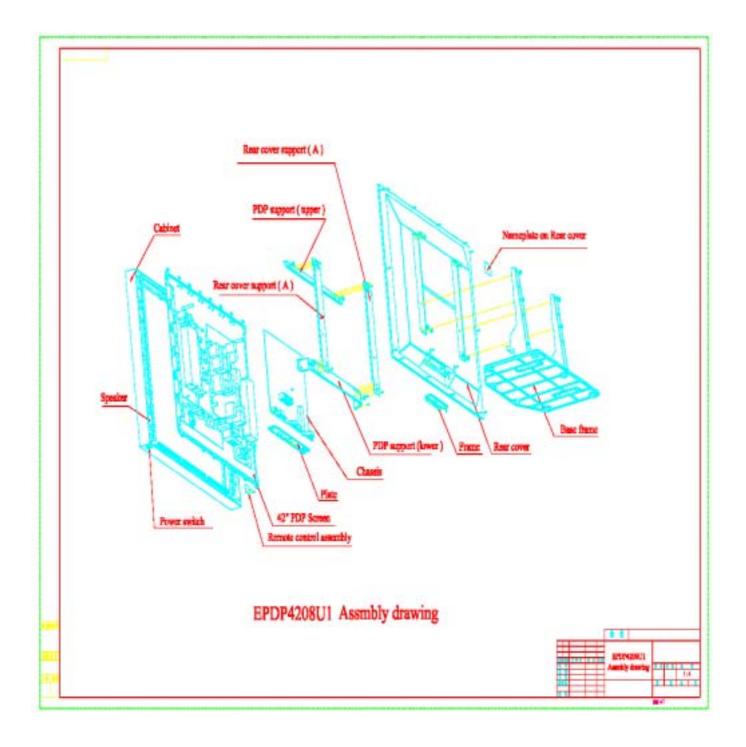

# 5.General assembly drawing

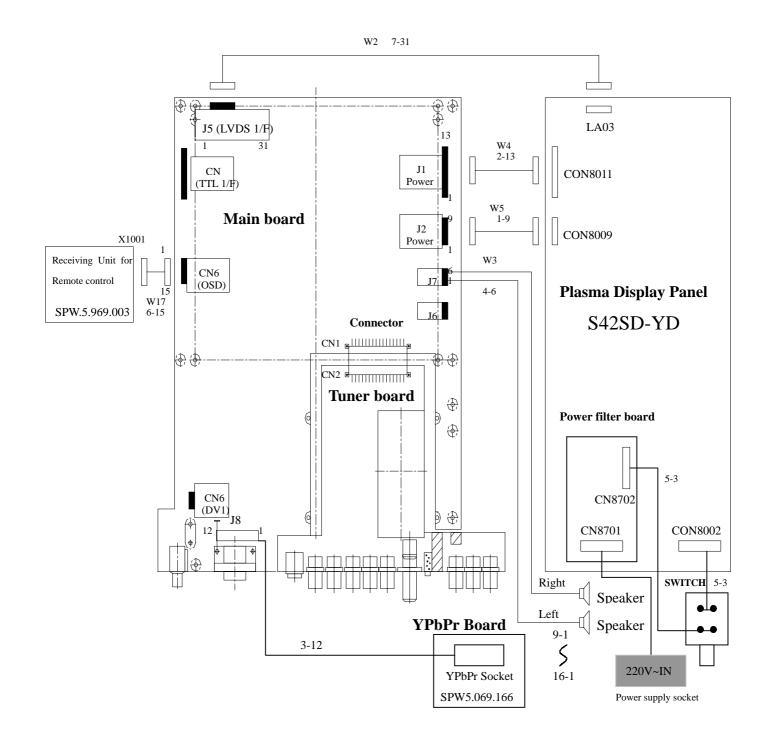

# 6.General connection diagram

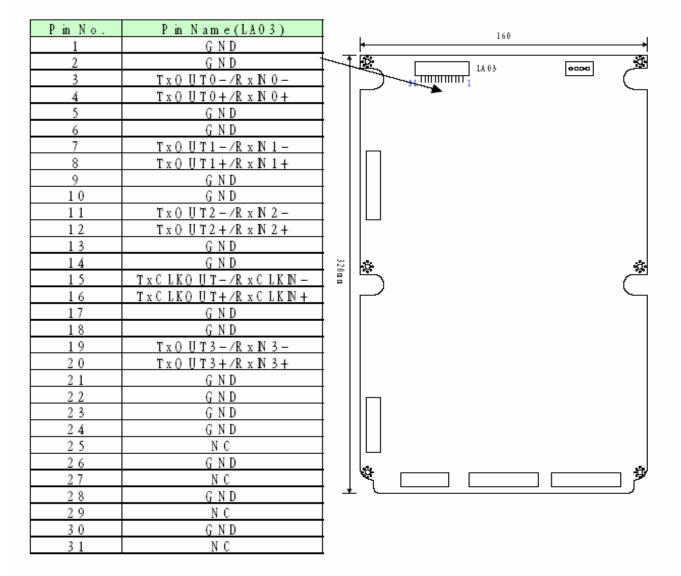

#### A. Specifications for the data signal of Plasma display panel

Input signal name and Pin assignment

|        | Connector Name: SA→J1(W4) |             |  |  |  |

|--------|---------------------------|-------------|--|--|--|

|        | to The Image              | Board       |  |  |  |

| Pin no | Voltage Source            | Usage       |  |  |  |

| 1      | 5Vsb                      | Vcc5-SB-PDP |  |  |  |

| 2      | GND                       | GND         |  |  |  |

| 3      | GND-D                     | GND         |  |  |  |

| 4      | B5d1                      | NC          |  |  |  |

| 5      | RELAY                     | PDP-RELAY   |  |  |  |

| 6      | TH-DET                    | NC          |  |  |  |

| 7      | FAN-DET                   | NC          |  |  |  |

| 8      | GND-A                     | GND         |  |  |  |

| 9      | GND-A                     | GND         |  |  |  |

| 10     | NC                        | NC          |  |  |  |

| 11     | V12A                      | NC          |  |  |  |

| 12     | V5a                       | Vcc5-PDP    |  |  |  |

| 13     | NC                        | NC          |  |  |  |

# **B. Input Power Voltage Source and Pin Assignment**

| C      | Connector Name: AUDIO→J2(W5) |               |  |  |

|--------|------------------------------|---------------|--|--|

|        | to The Audio Ar              | np Board      |  |  |

| Pin no | Voltage Source               | Usage         |  |  |

| 1      | V5A                          | Vcc5-PDP      |  |  |

| 2      | GND-A                        | GND           |  |  |

| 3      | 12VCC                        | Vcc12-FAN     |  |  |

| 4      | V9A                          | Vcc9-PDP      |  |  |

| 5      | GND-A                        | GND           |  |  |

| 6      | 24Vsp                        | Vcc12-AUD-PDP |  |  |

| 7      | 24Vsp                        | Vcc12-AUD-PDP |  |  |

| 8      | GNDS                         | GND-AUD       |  |  |

| 9      | GNDS                         | GND-AUD       |  |  |

|        | Connector Name:<br>OSD(W17) |  |  |

|--------|-----------------------------|--|--|

| Pin no | Usage                       |  |  |

| 1      | Vcc5                        |  |  |

| 2      | KPAD0                       |  |  |

| 3      | KPAD1                       |  |  |

| 4      | KPAD2                       |  |  |

| 5      | KPAD3                       |  |  |

| 6      | LED-RED                     |  |  |

| 7      | LED-GREEN                   |  |  |

| 8      | Vcc5-SB                     |  |  |

| 9      | GND                         |  |  |

| 10     | POWER-SW                    |  |  |

| 11     | IR                          |  |  |

| 12     | KPAD4                       |  |  |

| 13     | KPAD5                       |  |  |

| 14     | KPAD6                       |  |  |

| 15     | KPAD7                       |  |  |

| Connector Name:<br>SPEAKER(W3) |            |  |

|--------------------------------|------------|--|

| Pin no                         | Usage      |  |

| 1                              | SPEAKER-SW |  |

| 2                              | SPK-OUT1-  |  |

| 3                              | SPK-OUT1+  |  |

| 4                              | GND        |  |

| 5                              | SPK-OUT2-  |  |

| 6                              | SPK-OUT2+  |  |

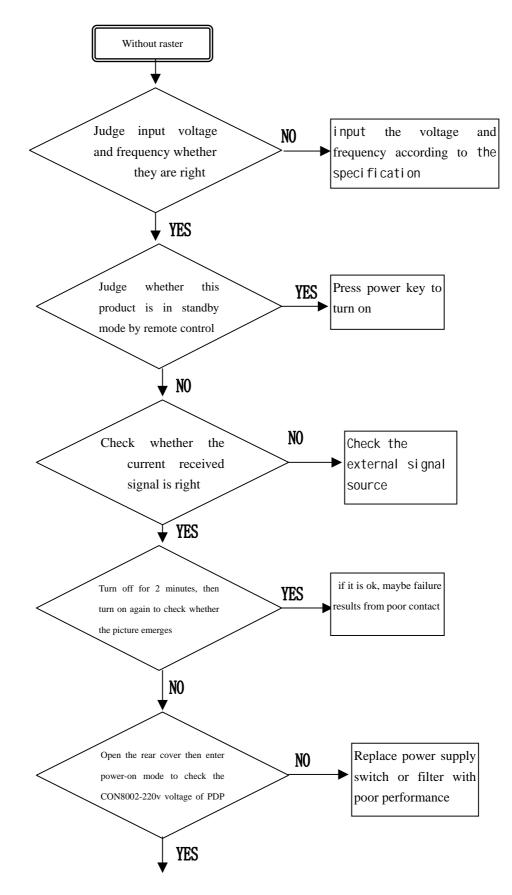

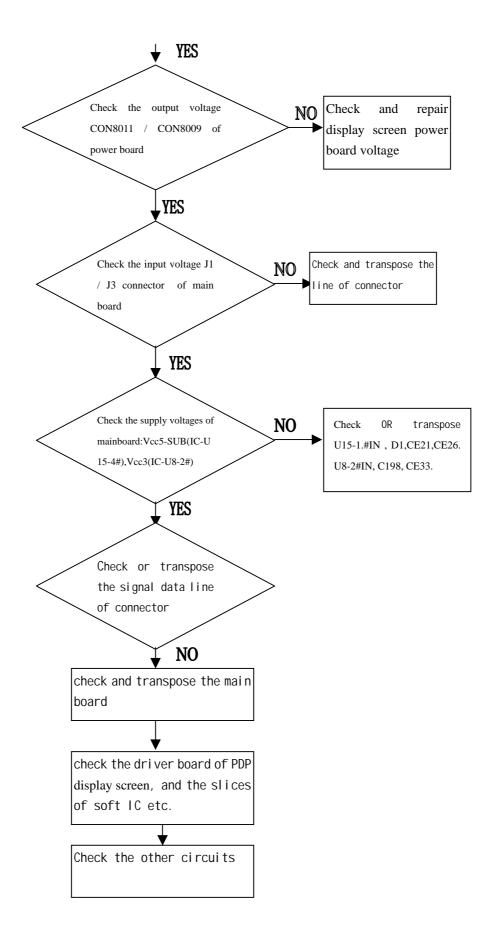

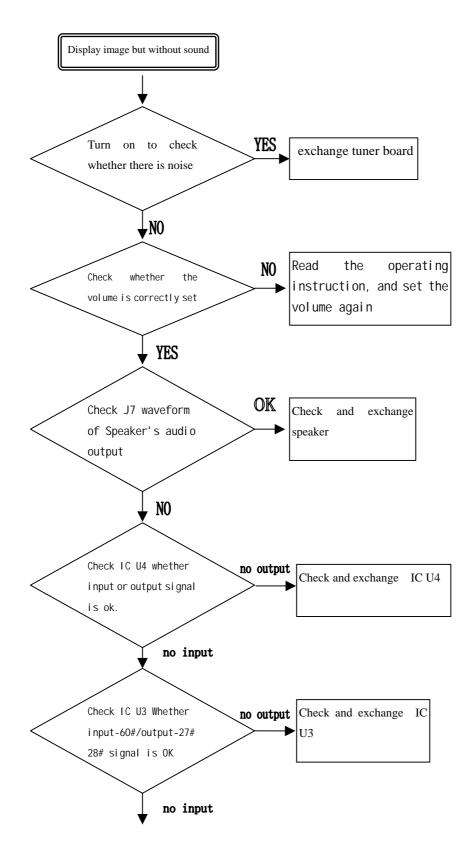

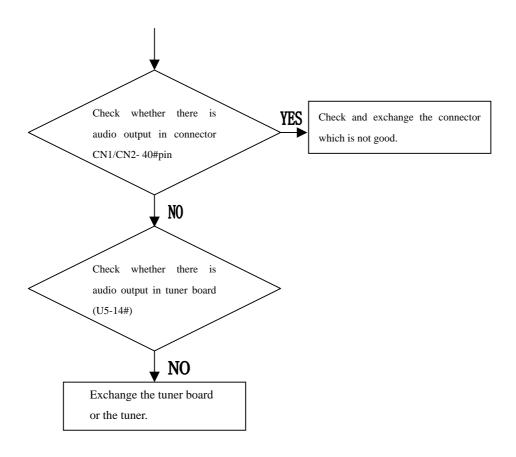

# 7.Failures analysis

# 8.Description of main ICs and components

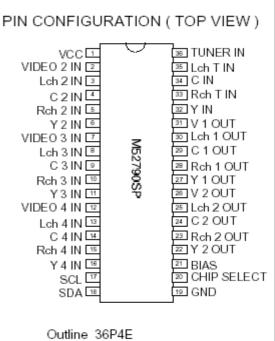

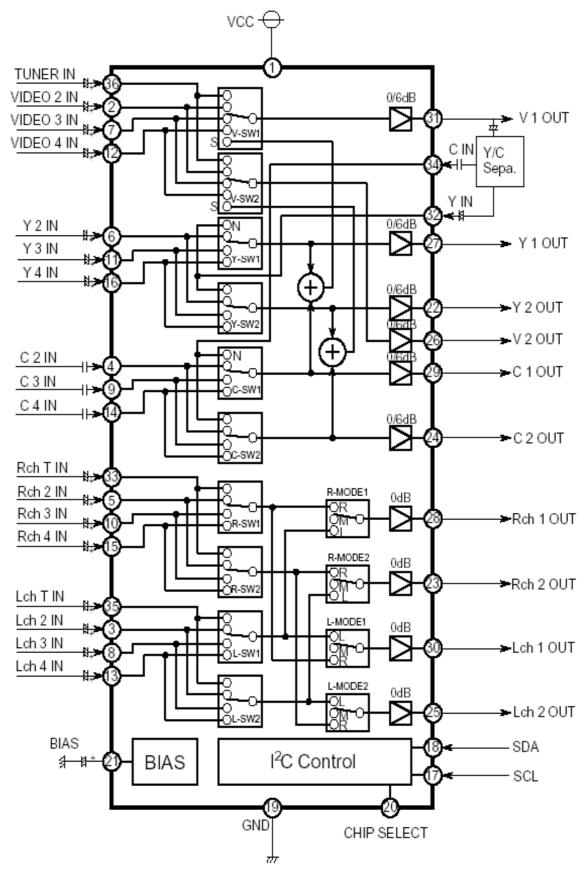

### (1) M52790SP/FP

### AV SWITCH with I<sup>2</sup>C BUS CONTROL

#### DESCRIPTION

The M52790 is AV switch semiconductor integrated circuit with  $I^2C$  bus control .

This IC contains 2-channels of 4-input audio switches and 2-channels of 4-input video switches. Each channel can be controled independently .

The video switches contain amplifiers can be controled a gain of

output 0dB or 6dB.

#### FEATURES

•Video and stereo sound switches in one package

•Wide frequency range (video switch) .....DC-20MHz •High separation ( video switch ).....Crosstalk -60dB ( typ. ) at 1MHz

•Two types of packages are provided : SDIP with a lead pitch of 1.778mm (M52790SP); and SSOP with a lead pitch of 0.8mm (M52790FP).

#### APPLICATION

Video equipment

#### **RECOMMENDED** CONDITION

**OPERATING**

Supply voltage 4.7V ~ 9.3V Rated supply voltage 5V,9V Maximum output current 63mA(at 9V)

### BLOCK DIAGRAM

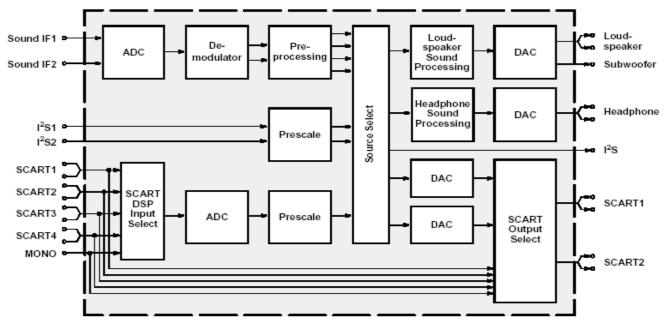

### (2) MSP3450G

#### Multistandard Sound Processor Family

Release Note: Revision bars indicate significant changes to the previous edition. The hardware and software description in this document is valid for the MSP 3450G version B5 and following versions.

#### Introduction

The MSP 3450G family of single-chip Multistandard Sound Processors covers the sound processing of all analog TV-Standards worldwide, as well as the NICAM digital sound standards. The full TV sound processing, starting with analog sound IF signal-in, down to processed analog AF-out, is performed on a single chip. Figure4 shows a simplified functional block diagram of the MSP 3450G.

This new generation of TV sound processing ICs now includes versions for processing the multichannel television sound (MTS) signal conforming to the standard recommended by the Broadcast Television Systems Committee (BTSC). The DBX noise reduction, or alternatively, MICRONAS Noise Reduction (MNR) is performed alignment free.

Other processed standards are the Japanese FM-FM multiplex standard (EIA-J) and the FM Stereo Radio standard.

Current ICs have to perform adjustment procedures in order to achieve good stereo separation for BTSC and EIA-J. The MSP 3450G has optimum stereo performance without any adjustments.

All MSP 3450G versions are pin and software downward-compatible to the MSP 3450D. The MSP 34x0G further simplifies controlling software. Standard selection requires a single I2C transmission only.

The MSP 34x0G has built-in automatic functions: The IC is able to detect the actual sound standard automatically (Automatic Standard Detection). Furthermore, pilot levels and identification signals can be evaluated internally with subsequent switching between mono/ stereo/bilingual; no I2C interaction is necessary (Automatic Sound Selection).

The ICs are produced in submicron CMOS technology. The MSP 34x0G is available in the following packages: PLCC68, PSDIP64, PSDIP52, PQFP80, and PLQFP64.

Fig. 4: Simplified functional block diagram of the MSP 3450G

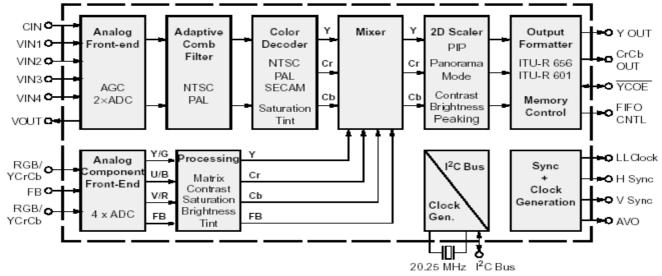

## (3) VPC323OD

#### PRELIMINARY DATA SHEET

#### **Comb Filter Video Processor**

#### Introduction

The VPC 3230D is a high-quality, single-chip video front-end, which is targeted for 4:3 and 16:9, 50/60-Hz and 100/120 Hz TV sets. It can be combined with other members of the DIGIT3000 IC family (such as DDP 331x) and/or it can be used with 3rd-party products.

The main features of the VPC 3230D are

- high-performance adaptive 4H comb filter Y/C separator with adjustable vertical peaking

- multi-standard color decoder PAL/NTSC/SECAM including all substandards

- four CVBS, one S-VHS input, one CVBS output

- two RGB/YCrCb component inputs, one Fast Blank (FB) input

- integrated high-quality A/D converters and associated clamp and AGC circuits

- multi-standard sync processing

- linear horizontal scaling (0.25 ... 4), as well as non-linear horizontal scaling 'Panoramavision'

- PAL+ preprocessing

- line-locked clock, data and sync, or 656-output interface

- peaking, contrast, brightness, color saturation and tint for RGB/YCrCb and CVBS/S-VHS

- high-quality soft mixer controlled by Fast Blank

- PIP processing for four picture sizes (1/4,1/9,1/16, or1/36 of normal size) with 8-bit resolution

- 15 predefined PIP display configurations and expert mode (fully programmable)

- control interface for external field memory

- I<sup>2</sup>C-bus interface

- one 20.25-MHz crystal, few external components

- 80-pin PQFP package

#### System Architecture

Fig.5 shows the block diagram of the video processor

Fig. 5: Block diagram of the VPC 3230D

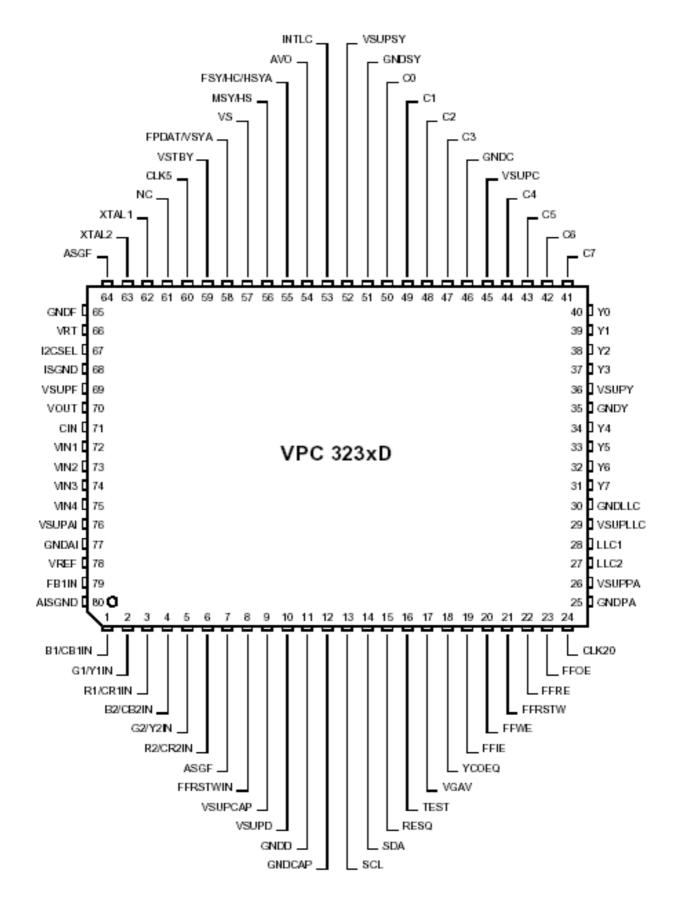

#### **Pin Configuration**

Fig.6: 80-pin PQFP package

### (4) Z86229

## **NTSC LINE 21 CCD DECODER**

### FEATURES

|         |                |                             |                                  |                                          | Automatic D       | Data Extraction |

|---------|----------------|-----------------------------|----------------------------------|------------------------------------------|-------------------|-----------------|

| Devices | Speed<br>(MHz) | Pin Count/<br>Package Types | Standard<br>Temp. Range          | On-Screen Display<br>& Closed Captioning | Program<br>Rating | Time of Day     |

| Z86229  | 12             | 18-Pin DIP, SOIC            | $0^{\circ}$ C to $+70^{\circ}$ C | Yes                                      | Yes               | Yes             |

- Complete Stand-Alone Line 21 Decoder for Closed-Captioned and Extended Data Services (XDS)

- Preprogrammed to Provide Full Compliance with EIA–608 Specifications for Extended Data Services

- Automatic Extraction and Serial Output of Special XDS Packets (Time of Day, Local Time Zone, and Program Blocking)

- Programmable XDS Filter for a Specific XDS Packet

- Cost-Effective Solution for NTSC Violence Blocking inside Picture-in-Picture (PiP) Windows

- Minimal Communications and Control Overhead Provide Simple Implementation of Violence Blocking, Closed Captioning, and Auto Clock Set Features

- Programmable, On-Screen Display (OSD) for Creating Full Screen OSD or Captions inside a Picture-in-Picture (PiP) Window

- User-Programmable Horizontal Display Position for easy OSD Centering and Adjustment

- I<sup>2</sup>C Serial Data and Control Communication

- Supports 2 Selectable I<sup>2</sup>C Addresses

#### GENERAL DESCRIPTION

Capable of processing Vertical Blanking Interval (VBI) data from both fields of the video frame in data, the Z86229 Line 21 Decoder offers a feature-rich solution for any television or set-top application. The robust nature of the Z86229 helps the device conform to the transmission format defined in the Television Decoder Circuits Act of 1990, and in accordance with the Electronics Industry Association specification 608 (EIA–608).

The Line 21 data streamcan consistof data fromseveral data channels multiplexed together. Field 1 consists of four data channels: two Captions and two Texts. Field 2 consists of five additional data channels: two Captions, two Texts, and Extended Data Services (XDS). The XDS data structure is defined in EIA–608. The Z86229 can recover and display data transmitted on any of these nine data channels.

The Z86229 can recover and output to a host processor via the I<sub>2</sub>C serial bus. The recovered XDS data packet is further defined in the EIA–608 specification. The on-chip XDS filters in the Z86229 are fully programmable, enabling recovery of only thoseXDSdata packets selected by the user. This functionality allows the device to extract the required XDS information with proper XDS filter setup for compatibility in a variety of TVs, VCRs, and Set-Top boxes.

In addition, the Z86229 is ideally suited to monitor Line 21 video displayed in a PiP window for violence blocking, CCD, and other XDS data services.

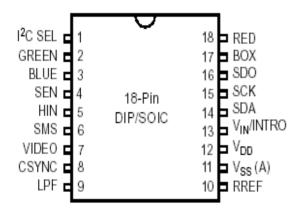

### PIN DESCRIPTION

Figure 2. Z86229 Pin Configuration

| No.  | Symbol                 | Function                           | Direction |

|------|------------------------|------------------------------------|-----------|

| 1    | I <sup>2</sup> C SEL   | I <sup>2</sup> C Address Selection | Input     |

| 2    | GREEN                  | Video Output                       | Output    |

| 3    | BLŲE                   | Video Output                       | Output    |

| 4    | SEN                    | Serial Enable                      | Input     |

| 5    | HIN                    | Horizontal In                      | Input     |

| 6    | SMS                    | Serial Mode Select                 | Input     |

| 7    | VIDEQ                  | Composite Video                    | Input     |

| 8    | CSYNC                  | Composite Sync                     | Output    |

| 9    | LPF                    | Loop Filter                        | Output    |

| 10   | RREF                   | Resistor Reference                 | Input     |

| 11   | V <sub>SS</sub> (A)    | Pwr. Supply (Analog)<br>GND        |           |

| 12   | $V_{DD}$               | Power Supply                       |           |

| 13   | V <sub>IN</sub> /INTRO | Vertical In/Interrupt Out          | In/Output |

| 14   | SDA                    | Serial Data                        | In/Output |

| 15   | SCK                    | Serial Clock                       | Input     |

| 16   | SDO                    | Serial Data Out                    | Output    |

| 17   | BQX                    | OSD Timing Signal                  | Output    |

| 18   | RED                    | Video Output                       | Output    |

| Note | : *DIP and SO          | IC pin configurations are identi   | cal.      |

Table 1. Z86229 Pin Identification\*

# **ABSOLUTE MAXIMUM RATINGS\***

| Symbol           | Parameter                                       | Value                        | Unit |

|------------------|-------------------------------------------------|------------------------------|------|

| VDD              | DC Supply Voltage                               | -0.5 to 6.0                  | v    |

| V <sub>IN</sub>  | DC Input Voltage                                | –0.5 to V <sub>DD</sub> +0.5 | v    |

| Vaut             | DC Output Voltage                               | -0.5 to V <sub>DD</sub> +0.5 | v    |

| I <sub>IN</sub>  | DC Input Current per Pin                        | + 10                         | mA   |

| lout             | DC Output Current per Pin                       | + 20                         | mA   |

| DD               | DC Supply Current                               | + 30                         | mA   |

| Ро               | Power Dissipation per Device                    | 300                          | mW   |

| T <sub>STG</sub> | Storage Temperature                             | -65 to +150                  | °C   |

| т                | Lead Temperature, 1 mm from Case for 10 seconds | 260                          | °C   |

Notes:

\*Voltages referenced to V<sub>SS</sub> (A). Values beyond the maximum ratings listed above may cause damage to the device. Functional operation should be restricted to the limits specified in the DC and AC Characteristics tables or Pin Description section.

## (5) HY57V641620HG

#### DRAM

### DESCRIPTION

The Hynix HY57V641620HG is a 67,108,864-bit CMOS Synchronous DRAM, ideally suited for the Mobile applications r which require low power consumption and extended temperature range. HY57V641620HG is organized as 4banks of 1,048,576x16.

HY57V641620HG is offering fully synchronous operation referenced to a positive edge of the clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL.

Programmable options include the length of pipeline (Read latency of 2 or 3), the number of consecutive read or write cycles initiated by a single control command (Burst length of 1,2,4,8 or Full page), and the burst count sequence(sequential or interleave). A burst of read or write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a new burst read or write command on any cycle. (This pipelined design is not restricted by a '2N' rule.)

### FEATURES

- Single 3.3±0.3V power supply Note)

Auto refresh and self refresh

- All device pins are compatible with LVTTL interface

4096 refresh cycles / 64ms

- JEDEC standard 400mil 54pin TSOP-II with 0.8mm of pin pitch

- Programmable Burst Length and Burst Type

- 1, 2, 4, 8 or Full page for Sequential Burst

- All inputs and outputs referenced to positive edge of system clock

- 1, 2, 4 or 8 for Interleave Burst

- Data mask function by UDQM or LDQM

- Programmable CAS Latency ; 2, 3 Clocks

Internal four banks operation

### ORDERING INFORMATION

| Part No.                     | Clock Frequency    | Power     | Organization    | Interface | Package              |  |

|------------------------------|--------------------|-----------|-----------------|-----------|----------------------|--|

| HY57V641620HGT-5I/55I/6I/7I  | 200/183/166/143MHz |           |                 |           |                      |  |

| HY57V641620HGT-KI            | 133MHz             |           |                 |           |                      |  |

| HY57V641620HGT-HI            | 133MHz             | Normal    |                 |           |                      |  |

| HY57V641620HGT-8I            | 125MHz             | Normai    |                 |           |                      |  |

| HY57V641620HGT-PI            | 100MHz             |           |                 |           |                      |  |

| HY57V641620HGT-SI            | 100MHz             |           | 4Banks x 1Mbits | LVTTL     | 400mil 54pin TSOP II |  |

| HY57V641620HGLT-5I/55I/6I/7I | 200/183/166/143MHz |           | x16             | LVIIL     | 400mi 34pm 100Pm     |  |

| HY57V641620HGLT-KI           | 133MHz             |           |                 |           |                      |  |

| HY57V641620HGLT-HI           | 133MHz             | Low power |                 |           |                      |  |

| HY57V641620HGLT-8I           | 125MHz             | Low power |                 |           |                      |  |

| HY57V641620HGLT-PI           | 100MHz             | 1         |                 |           |                      |  |

| HY57V641620HGLT-SI           | 100MHz             |           |                 |           |                      |  |

Note : VDD(Min) of HY57V641620HG(L)T-5I/55I/6I is 3.135V

#### PIN CONFIGURATION

### PIN DESCRIPTION

| PIN          | PIN NAME                                                                                                | DESCRIPTION                                                                                                                           |

|--------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| CLK          | Clock                                                                                                   | The system clock input. All other inputs are registered to the SDRAM on the rising edge of CLK                                        |

| CKE          | Clock Enable                                                                                            | Controls internal clock signal and when deactivated, the SDRAM will be one<br>of the states among power down, suspend or self refresh |

| CS           | Chip Select                                                                                             | Enables or disables all inputs except CLK, CKE and DQM                                                                                |

| BA0,BA1      | Bank Address                                                                                            | Selects bank to be activated during RAS activity<br>Selects bank to be read/written during CAS activity                               |

| A0 ~ A11     | Address                                                                                                 | Row Address : RA0 ~ RA11, Column Address : CA0 ~ CA7<br>Auto-precharge flag : A10                                                     |

| RAS, CAS, WE | VE Row Address Strobe,<br>Column Address Strobe,<br>Write Enable Refer function truth table for details |                                                                                                                                       |

| LDQM, UDQM   | Data Input/Output Mask                                                                                  | Controls output buffers in read mode and masks input data in write mode                                                               |

| DQ0 ~ DQ15   | Data Input/Output                                                                                       | Multiplexed data input / output pin                                                                                                   |

| VDD/VSS      | Power Supply/Ground                                                                                     | Power supply for internal circuits and input buffers                                                                                  |

| VDDQ/VSSQ    | Data Output Power/Ground                                                                                | Power supply for output buffers                                                                                                       |

| NC           | No Connection                                                                                           | No connection                                                                                                                         |

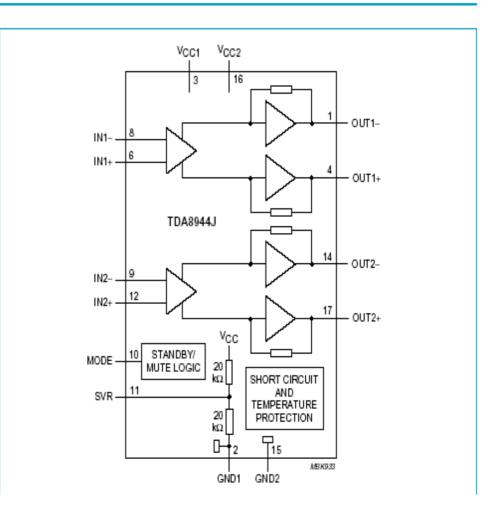

### (6) TDA8944J

#### STEREO AUDIO AMPLIFIER

# 1. General description

The TDA8944J is a dual-channel audio power amplifier with an output power of  $2 \times 7$  W at an 8  $\Omega$  load and a 12 V supply. The circuit contains two Bridge Tied Load (BTL) amplifiers with an all-NPN output stage and standby/mute logic. The TDA8944J comes in a 17-pin DIL-bent-SIL (DBS) power package. The TDA8944J is printed-circuit board (PCB) compatible with all other types in the TDA894x family. One PCB footprint accommodates both the mono and the stereo products.

# 2. Features

- Few external components

- Fixed gain

- Standby and mute mode

- No on/off switching plops

- Low standby current

- High supply voltage ripple rejection

- Outputs short-circuit protected to ground, supply and across the load

- Thermally protected

- Printed-circuit board compatible.

# 3. Applications

- Mains fed applications (e.g. TV sound)

- PC audio

- Portable audio.

# 4. Quick reference data

#### Table 1: Quick reference data

| Symbol           | Parameter                | Conditions                        | Min | Тур | Max | Unit |

|------------------|--------------------------|-----------------------------------|-----|-----|-----|------|

| Vcc              | supply voltage           |                                   | 6   | 12  | 18  | V    |

| lq               | quiescent supply current | $V_{CC}$ = 12 V; $R_L$ = $\infty$ | -   | 24  | 36  | mΑ   |

| l <sub>stb</sub> | standby supply current   |                                   | -   | -   | 10  | μA   |

| Table 1: | Quick reference datac              | onunuea                                                    |     |      |     |      |

|----------|------------------------------------|------------------------------------------------------------|-----|------|-----|------|

| Symbol   | Parameter                          | Conditions                                                 | Min | Тур  | Max | Unit |

| Po       | output power                       | THD = 10%; R <sub>L</sub> = 8 Ω;<br>V <sub>CC</sub> = 12 V | 6   | 7    | -   | W    |

| THD      | total harmonic distortion          | P <sub>o</sub> = 1 W                                       | -   | 0.03 | 0.1 | %    |

| Gv       | voltage gain                       |                                                            | 31  | 32   | 33  | dB   |

| SVRR     | supply voltage ripple<br>rejection |                                                            | 50  | 65   | -   | dB   |

| Table 1: | Quick | reference d | atacontinued |

|----------|-------|-------------|--------------|

|----------|-------|-------------|--------------|

# 5. Ordering information

| Type number | Package |                                                                     |          |  |  |  |

|-------------|---------|---------------------------------------------------------------------|----------|--|--|--|

|             | Name    | Description                                                         | Version  |  |  |  |

| TDA8944J    | DBS17P  | plastic DIL-bent-SIL power package;<br>17 leads (lead length 12 mm) | SOT243-1 |  |  |  |

# 6. Block diagram

Fig 9. Block diagram

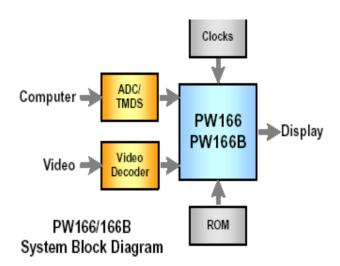

### (7) PW166 ImageProcessor

XGA/SXGA Flat Panel Display Controller IC

# General

The PW166/PW166B ImageProcessor is a highly integrated "system-on-a-chip" that interfaces analog, digital, and video inputs in virtually any format to a digital projection system or multimedia display. The PW166/PW166B is pin-compatible with the PW164.

An embedded SDRAM frame buffer and memory controller perform frame rate conversion. Computer images from VGA to UXGA at almost any refresh rate can be resized to fit on a fixedfrequency target display device with any resolution up to SXGA with full 24-bit color.

The PW166/PW166B includes advanced second generation image scaling that provides completely programmable, horizontal and vertical image scaling. Keystoning allows vertical keystoning effects. In addition, non-linear scaling is supported for precise scaling control, with 16:9 aspect ration sources and displays. This high-quality scaling—coupled with Auto Image Optimization circuitry—provides sharp, full-screen images, centered on the screen, with no manual adjustments required.

The PW166/PW166B also includes advanced secondgeneration sync decoding which provides full support for a wide variety of sync types. This includes interlaced, progressive, sync-on-green, and TMDS DE (Data Enable) only.

The PW166/PW166B ImageProcessor supports NTSC or PAL video data with a 4:3 aspect ratio and 16:9 aspect ratio sources, such as DVD or HDTV. Nonlinear scaling and separate horizontal and vertical scalers allow these inputs to be resized optimally for the native resolution and aspect ratio of the display device.

The PW166B uses an integrated PLL to synchronize the display interface timing to the input timing. This requires only a single external crystal to generate all necessary clocks for the system (PW166B only).

An integrated OSD controller provides bit-mapped based OSDs with 16 colors from a 64K color palette. The OSD controller supports transparent and translucent functions.

The PW166/PW166B provides a Pulse Width Modulation (PWM) output for low cost backlight or audio control.

With reference source code and an on-chip microprocessor, manufacturers can develop feature-rich products with rapid timeto-market. Programmable features include the user interface, custom start-up screen, all automatic imaging features, and special screen effects.

# Features

- · Second-Generation Image Scaling

- · Second-Generation Automatic Image Optimization

- Video Processing

- · Picture-in-Picture (PIP)

- Frame Rate Conversion

- · Multi-region, non-linear scaling

- Color Matrix for improved color temperature adjustment

- On-board PLLs to generate MCLK and DCLK (PW166B only)

- On-Screen Display

- On-Chip Microprocessor

- JTAG Debugging Port

- Hardware PWM Output

# Applications

- Flat Panel Monitors

- · Digital Projection Systems

- Multimedia Displays

| Device                    | Application                                   | Package  |

|---------------------------|-----------------------------------------------|----------|

| PW166-10T<br>PW166B-10T   | Up to SXGA in, SVGA/XGA<br>out, no keystone   |          |

| PW166-10TK<br>PW166B-10TK | Up to SXGA in, SVGA/XGA<br>out, with keystone | 256 PBGA |

| PW166-20T<br>PW166B-20T   | Up to UXGA in, SXGA out,<br>no keystone       | 230 FBOA |

| PW166-20TK<br>PW166B-20TK | Up to UXGA in, SXGA out,<br>with keystone     |          |

| 20 | GBE6       | GGO2       | 6603       | GGO7        | GGE2        | G<br>COAST  | GPEN<br>SOG | GGE4 | GGE6 | GRO0       | GRO4       | GRE0      | GRE4 | GRE5        | GRE7 | DRE1 | VDD<br>3.3 | DRE7        | DGE2       | DGE4       |

|----|------------|------------|------------|-------------|-------------|-------------|-------------|------|------|------------|------------|-----------|------|-------------|------|------|------------|-------------|------------|------------|

| 19 | GBE4       | GBE5       | 6601       | GG06        | GGE1        | GBLK<br>SPL | GHS         | GCLK | GGE5 | GGE7       | GR03       | GR07      | GRE1 | GRE6        | DRE0 | VSS  | DRE5       | DGE1        | DGE3       | DBE0       |

| 18 | GBE 1      | GBE3       | VDD<br>3.3 | GBE7        | GGO4        | GGE0        | VDD<br>2.6  | GREF | GGE3 | VDD<br>2.5 | GRO2       | GR05      | GRE2 | VDD<br>2.5  | DRE2 | DRE4 | DGE0       | VDD<br>3.3  | DGE7       | DBE1       |

| 17 | GBO5       | GBO7       | GBE2       | VSS         | GGO0        | GGO5        | VSS         | GEBK | GVS  | VSS        | GRO1       | GR06      | GRE3 | VSS         | DRE3 | DRE6 | VSS        | DGE5        | VSS        | VDD<br>3.3 |

| 16 | GBO1       | GBO4       | GBO6       | GBE0        |             |             |             |      |      |            |            |           |      |             |      |      | DGE6       | DBE2        | DBE6       | DBE 4      |

| 15 | V<br>FIELD | GBO0       | GBO2       | GBO3        |             |             |             |      |      |            |            |           |      |             |      |      | DBE3       | DBE5        | DBE7       | DEN        |

| 14 | ws         | VHS        | VDD<br>2.5 | VSS         |             |             |             |      |      |            |            |           |      |             |      |      | VSS        | VDD<br>2.5  | VSS        | VDD<br>2.5 |

| 13 | MODE<br>0  | VB7        | VPEN       | CPU<br>TMS  |             |             |             |      |      |            |            |           |      |             |      |      | DHS        | DVS         | MCK<br>EXT | DCK<br>EXT |

| 12 | VSS        | VDD<br>2.5 | VB6        | VCLK        |             |             |             |      |      |            |            |           |      |             |      |      | VSS        | VDD<br>3.3  | DCLK       | DR00       |

| 11 | VB5        | VSS        | VDD<br>2.5 | VB4         |             |             |             |      |      |            |            |           |      |             |      |      | VSS        | VDD<br>2.5  | DR01       | DR02       |

| 10 | VB3        | VB2        | VDD<br>2.5 | VSS         |             |             |             |      |      |            |            |           |      |             |      |      | DR03       | DRO4        | DR05       | DR06       |

| 9  | VB1        | VBO        | VG6        | VG5         |             |             |             |      |      |            |            |           |      |             |      |      | VSS        | VDD<br>3.3  | DR07       | DGO0       |

| 8  | VG7        | VG4        | VG1        | VG0         |             |             |             |      |      |            |            |           |      |             |      |      | DGO3       | DG02        | DG01       | DGO4       |

| 7  | VG3        | VG2        | VDD<br>3.3 | VSS         |             |             |             |      |      |            |            |           |      |             |      |      | VSS        | VDD<br>2.6P | DG06       | DGO5       |

| 6  | CPU<br>TCK | MODE<br>2  | PORT<br>B5 | PORT<br>B2  |             |             |             |      |      |            |            |           |      |             |      |      | DBO1       | DB00        | VSS        | VDD<br>3.3 |

| Б  | PORT<br>B7 | PORT<br>B6 | PORT<br>B1 | PORT<br>A5  |             |             |             |      |      |            |            |           |      |             |      |      | Mode<br>1  | DBO4        | DBO2       | DGO7       |

| 4  | PORT<br>B4 | PORT<br>B3 | PORT<br>A4 | VSS         | IR<br>RCVR0 | D0          | VSS         | D8   | D13  | VSS        | VSS        | WR        | A3   | XTAL<br>OUT | A11  | A16  | VSS        | DB06        | VSS        | DB03       |

| 3  | PORT<br>B0 | PORT<br>A6 | VDD<br>2.5 | TXD         | RESET       | D1          | VDD<br>2.6  | D9   | D14  | VDD<br>3.3 | VDD<br>2.5 | RD        | A2   | XTAL<br>IN  | A8   | A12  | A17        | VDD<br>3.3  | CPU<br>TDO | DB05       |

| 2  | PORT<br>A7 | PORT<br>A2 | PORT<br>A0 | IR<br>RCVR1 | EXT<br>INT  | D3          | D5          | D10  | D12  | RAM<br>WE  | ROM<br>WE  | CS0       | BHEN | A1          | A5   | A7   | A10        | A15         | A19        | DBO7       |

| 1  | PORT<br>A3 | PORT<br>A1 | RXD        | NMI         | D2          | D4          | D6          | D7   | D11  | D15        | RAM<br>OE  | ROM<br>OE | CS1  | AD          | A4   | Aß   | A9         | A13         | A14        | A18        |

|    | А          | В          | С          | D           | E           | F           | G           | н    | J    | к          | L          | М         | N    | Р           | R    | т    | U          | ٧           | w          | Ŷ          |

Fig11.PW166 Pin Diagram - Top View

# ImageProcessor Pin Descriptions

| Name    | Pin(s) | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|---------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|         |        |      | Graphics Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| GCLK    | H19    | ID   | Graphics port pixel clock input. Typically driven by an external PLL GPort Clock. The GCLK pin can<br>be selected to be the source for the internal GCLK that is used for GPort image capture and for the<br>PLL divider (see GCKPOL & GCKSRC bits).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| GPENSOG | G20    | ID   | Graphics port pixel enable input. Used for external flow control when EXTFCE=1. When GPENSOG is<br>high, input RGB pixel is valid. Using GPENSOG allows capture of non-contiguous data. When<br>EXTFCE=0, this is the Graphics port Sync-On-Green (SOG) input. Driven by external sync stripper<br>circuit, this pin is monitored (SOGACT status bit) and can supply composite sync information<br>(depending on SOGEN & COMPEN bits).                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| GVS     | J17    | D    | phics port vertical sync input. Indicates start of next field or frame of input data. GVS can be either<br>e-high or active-low as determined by VPOL and VSOK. GVS is not used when a composite<br>al sync source is used (SOGEN=1 or COMPEN=1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| GHS     | G19    | D    | Graphics port horizontal sync input. Indicates the start of the next line of input data. This signal is<br>internally polarity corrected and monitored for composite sync content (HSOK, HPOL, & COMP status<br>bits). GHS can supply horizontal sync information or digital composite sync information (depending on<br>COMPEN bit). GHS is also used as the input to the clock phase delay circuit that produces the GREF<br>signal.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| GFBK    | H17    | I/O  | Graphics port PLL feedback / line advance input. This pin has three different functions depending on the register settings for EXTFBK and EXTFCE:        EXTFBK EXTFCE        O      X      GFBKOUT: An output from the internal PLL divider.        0      X      GFBKIN: An input to the feedback pulse from an external PLL divider. In free running capture mode this signal is used to define the horizontal capture region (along with CAPL and CAPW), and advances the GPort capture controller to the next input line. The LAVPOL bit is used to select the polarity of GFBKIN.        1      1      GLAV: An input to the graphics port line advance. Used in external flow control capture mode. When GLAV transitions (depending on LAVPOL bit), the GPort capture controller advances to the next input line. |  |  |  |  |  |  |

| GRE0    | M20    | D    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| GRE1    | N19    | ID   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| GRE2    | N18    | D    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| GRE3    | N17    | D    | Graphics port red even data sub-pixel input. Red channel data for single pixel mode or even red pixel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| GRE4    | N20    | D    | data for dual pixel input mode. Pr channel data for YPbPr inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| GRE5    | P20    | D    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| GRE6    | P19    | ID   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| GRE7    | R20    | D    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| GGE0    | F18    | ID   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| GGE1    | E19    | ID   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| GGE2    | E20    | D    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| GGE3    | J18    | ID   | Graphics port green even data sub-pixel input. Green channel data for single pixel mode or even                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| GGE4    | H20    | D    | green pixel data for dual pixel input mode. Y channel data for YPbPr inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| GGE5    | J19    | D    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| GGE6    | J20    | ID   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| GGE7    | K19    | D    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Name         | Pin(s)     | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|--------------|------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| GBE0         | D16        | ID    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GBE1         | A18        | ID    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GBE2         | C17        | D     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GBE3         | B18        | ID    | Graphics port blue even data sub-pixel input. Blue channel data for single pixel mode or even blue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| GBE4         | A19        |       | pixel data for dual pixel input mode. Pb channel data for YPbPr inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| GBE5         | B19        | D     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GBE6         | A20        | ID ID |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GBE7         | D18        | D     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GRO0         | K20        | ID    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GR01         | L17        | ID ID |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GRO2         | L18        | D     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GRO3         | L19        | ID    | Graphics port red odd data sub-pixel input. Not used for single pixel mode, odd red pixel data for dual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| GRO4         | L20        |       | pixel input mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| GRO5         | M18        |       | production in part of the second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GRO6         | M17        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GRO6<br>GRO7 | M19        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GGO0         | E17        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GG01         | C19        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |