# SERVICE MANUAL 17MB95S

15.11.2012

## **Table of Contents**

| 1.  | INT  | RODUCTION                                   |

|-----|------|---------------------------------------------|

| 2.  | TUI  | NER                                         |

| 3.  | AU   | DIO AMPLIFIER STAGES                        |

| Α   | . N  | IAIN AMPLIFIER (TAS5719)(6-8 W option)    7 |

| В   | . N  | MAIN AMPLIFIER (TS4962M)(2.5 W option)      |

| С   | . н  | EADPHONE AMPLIFIER STAGE                    |

| 4.  | POV  | WER STAGE                                   |

| 5.  | MIC  | CROCONTROLLER (MSTAR MSD8WB9BX)             |

| 6.  | 1Gb  | DDR3 SDRAM                                  |

| 7.  | 1Gb  | G-die DDR3 SDRAM                            |

| 8.  | 2Gb  | it (256M x 8 bit) NAND Flash Memory         |

| 9.  |      | 1-BIT [16M x 1] CMOS SERIAL FLASH EEPROM    |

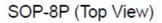

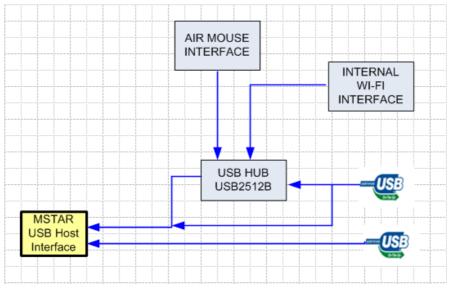

| 10. | USE  | 3 Interface                                 |

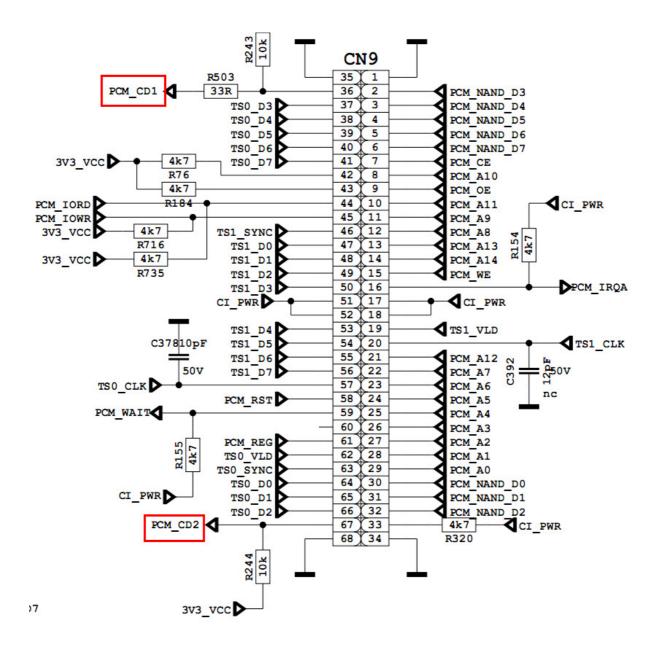

| 11. | CII  | nterface                                    |

| 12. | Soft | ware Update                                 |

| 13. | Tro  | ubleshooting                                |

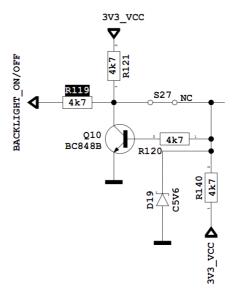

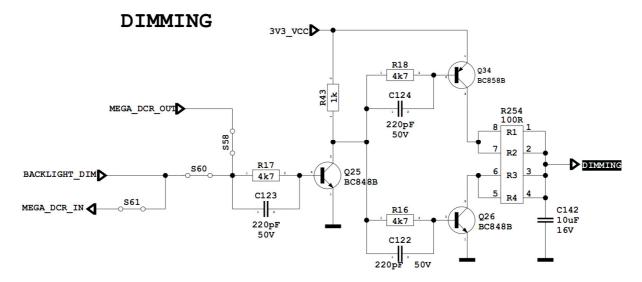

|     | A.   | No Backlight Problem                        |

|     | B.   | CI Module Problem                           |

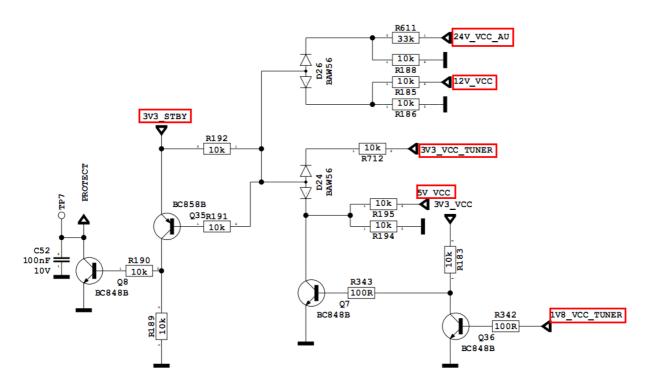

|     | C.   | Staying in Stand-by Mode                    |

|     | D.   | IR Problem                                  |

|     | E.   | Keypad Touchpad Problems                    |

|     | F.   | USB Problems                                |

|     | G.   | No Sound Problem                            |

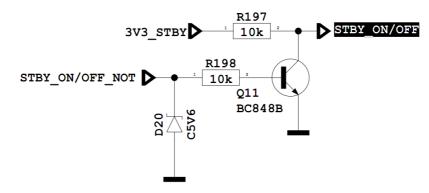

|     | H.   | Standby On/Off Problem                      |

|     | I.   | No Signal Problem                           |

| 14. | Serv | vice Menu Settings                          |

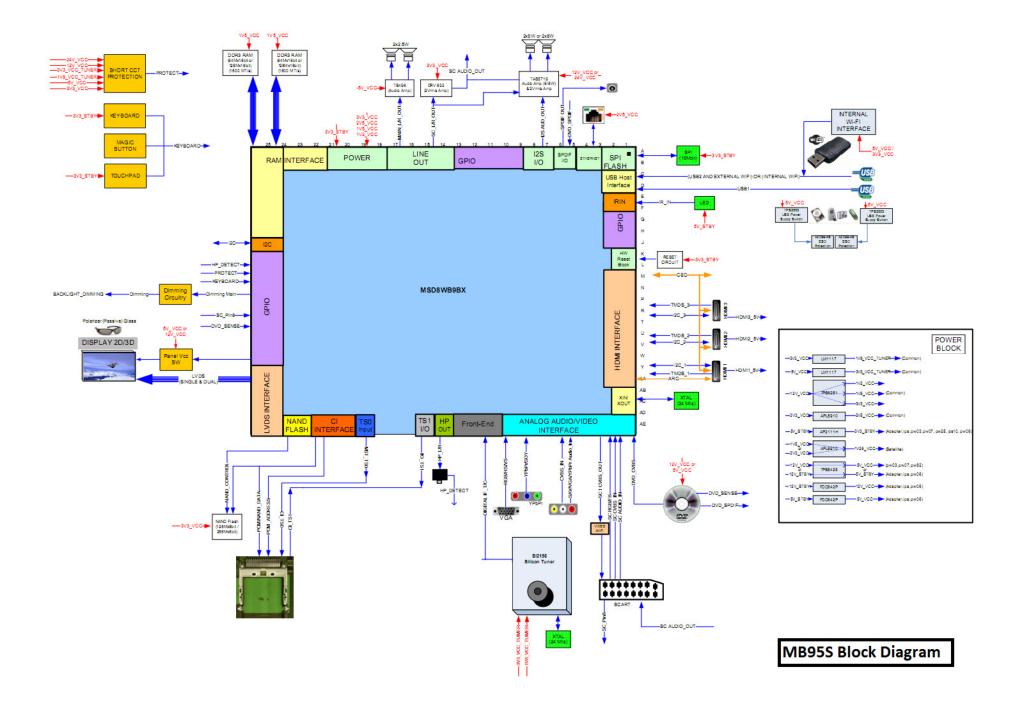

| 15. | Gen  | eral Block Diagram                          |

# **1. INTRODUCTION**

17MB95S main board is driven by MStar SOC. This IC is a single chip iDTV solution that supports channel decoding, MPEG decoding, and media-center functionality enabled by a high performance AV CODEC and CPU.

Key features includes,

- Combo Front-End Demodulator

- A multi standart A/V format decoder

- The MACEpro video processor

- Home theatre sound processor

- Internet and Variety of Connectivity Support

- Dual-stream decoder for 3D contents

- Mılti-purpose CPU for OS and multimedia

- Peripheral and power management

Supported peripherals are:

- 1 RF input VHF I, VHF III, UHF

- 1 Side AV (CVBS, R/L\_Audio)

- 1 SCART socket(Common)

- 1 Side YPbPr

- 1 Side S-Video(Common)

- 1 PC input(Common)

- 3 HDMI input

- 1 Common interface(Common)

- 1 S/PDIF output

- 1 Headphone(Common)

- 2 USB

- 1 Ethernet-RJ45

- 1 External Touchpad(Common)

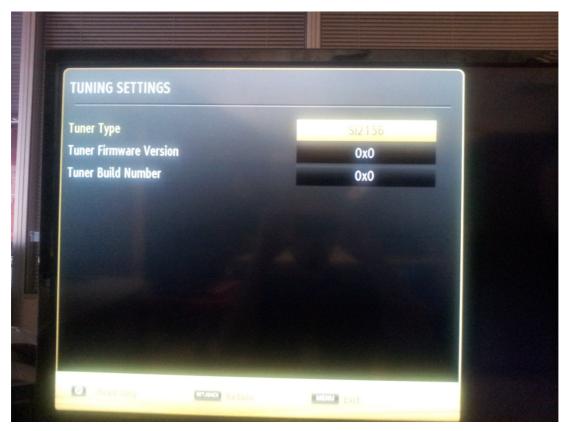

#### 2. TUNER

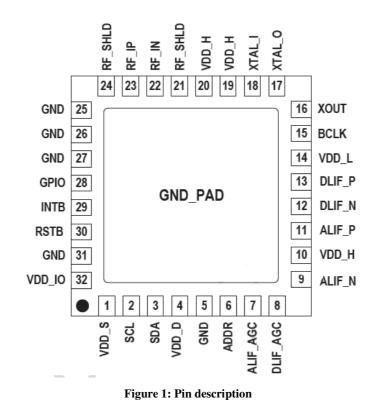

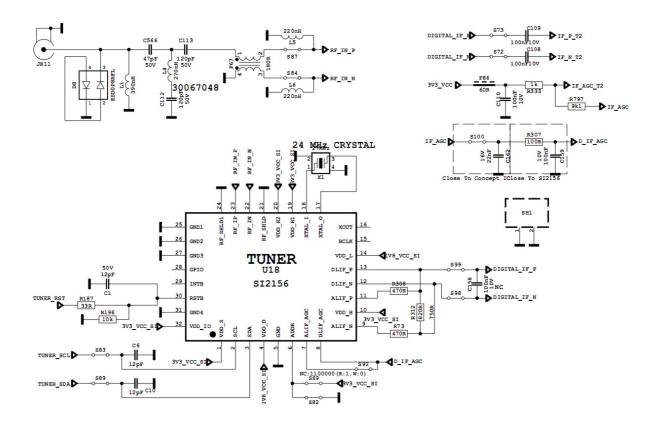

#### A. SI2156 Terrestrial and Cable TV Tuner:

#### A.1. Description:

The Si2156 integrates a complete hybrid TV tuner supporting all worldwide terrestrial and cable TV standards. Leveraging Silicon Labs' field proven digital low-IF architecture, the Si2156 maintains the unmatched performance and design simplicity of the Si2153 while further reducing footprint size and bill of materials cost. No external LNAs, tracking filters, wirewound inductors, or SAW filters are used.

Compared with competing silicon tuners and discrete MOPLL-based tuners, the Si2156 delivers superior picture quality and a higher number of received stations in crowded and near/far real-world reception conditions. The high linearity and low noise RF front-end delivers superior blocking performance and higher sensitivity in the presence of strong undesired channels and interference.

The Si2156 integrates the complete signal path from antenna input to IF outputs for both analog and digital transmission standards. Compared to traditional discrete MOPLL-based tuners, the Si2156 eliminates hundreds of external components including external LNAs, tracking filter varactors and inductors (unlike competing silicon tuners), and SAW filters, resulting in the simplest, lowest-cost BOM for a hybrid TV tuner.

Interfacing the Si2156 seamlessly with the Si2165 DVB-T/C demodulator creates a complete terrestrial and cable DVB-T/C receiver plus PAL/SECAM tuner.

#### A.2. Features:

- Worldwide hybrid TV tuner

- Analog TV: NTSC, PAL/SECAM

- Digital TV: ATSC/QAM, DVB-T/C, ISDB-T/C, DTMB

- 42-1002 MHz frequency range

- Compliance to A/74, NorDig, D-Book, C-Book, ARIB, EN55020, OpenCable<sup>™</sup> specifications

- Best-in-class real-world reception

- Exceeds discrete MOPLL-based tuners

- Highly integrated, lowest BOM

- No SAW filters or wirewound inductors required

- Integrated LNAs and complete tracking filters

- No alignment, tuning or calibration required

- Digital low-IF architecture

- Integrated channel select filters

- Flexible output interface

- ALIF to analog TV demodulator or SoC

- DLIF to digital TV demodulator or SoC

- 3.3 and 1.8 V power supplies

- Standard CMOS process technology

- 5 x 5 mm, 32-pin QFN package

- RoHS compliant

| Pin Number(s) | Name     | I/O | Description                                                                                |  |

|---------------|----------|-----|--------------------------------------------------------------------------------------------|--|

| 1             | VDD_S    | S   | Interface supply voltage (I <sup>2</sup> C), 1.8 to 5.0 V                                  |  |

| 2             | SCL      | Ι   | I <sup>2</sup> C clock input                                                               |  |

| 3             | SDA      | I/O | I <sup>2</sup> C data input/output                                                         |  |

| 4             | VDD_D    | S   | Digital supply voltage, 1.8 ∨                                                              |  |

| 5             | GND      | S   | Ground. Connect GND pins to GND_PAD.                                                       |  |

| 6             | ADDR     | Ι   | I <sup>2</sup> C address select                                                            |  |

| 7*            | ALIF_AGC | I   | ALIF output amplitude control input (optional)                                             |  |

| 8*            | DLIF_AGC | I   | DLIF output amplitude control input (optional)                                             |  |

| 9*            | ALIF_N   | 0   | ALIF differential output to ATV demodulator (negative)                                     |  |

| 10            | VDD_H    | S   | Analog high supply voltage, 3.3 V                                                          |  |

| 11*           | ALIF_P   | 0   | ALIF differential output to ATV demodulator (positive)                                     |  |

| 12*           | DLIF_N   | 0   | DLIF differential output to DTV demodulator (negative)                                     |  |

| 13*           | DLIF_P   | 0   | DLIF differential output to DTV demodulator (positive)                                     |  |

| 14            | VDD_L    | S   | Analog low supply voltage, 1.8 V                                                           |  |

| 15*           | BCLK     | 0   | Buffered clock output                                                                      |  |

| 16*           | XOUT     | 0   | Output reference clock to secondary tuner or receiver                                      |  |

| 17            | XTAL_O   | S   | Crystal pin 2 (leave floating if XTAL_I is driven by XOUT of<br>another tuner or receiver) |  |

| 18            | XTAL_I   | 1   | Crystal pin 1 (or RCLK input driven by XOUT of another tuner or receiver)                  |  |

| 19            | VDD_H    | S   | Analog high supply voltage, 3.3 V                                                          |  |

| 20            | VDD_H    | s   | Analog high supply voltage, 3.3 V                                                          |  |

| 21            | RF_SHLD  | s   | RF input shield                                                                            |  |

| 22            | RF_IN    | Ι,  | RF balanced input from balun (negative)                                                    |  |

| 23            | RF_IP    |     | RF balanced input from balun (positive)                                                    |  |

| 24            | RF_SHLD  | S   | RF input shield                                                                            |  |

| 25            | GND      | S   | Ground. Connect GND pins to GND_PAD.                                                       |  |

| 26            | GND      | S   | Ground. Connect GND pins to GND_PAD.                                                       |  |

| 27            | GND      | S   | Ground. Connect GND pins to GND_PAD.                                                       |  |

| 28*           | GPIO     | I/O | General purpose input/output                                                               |  |

| 29*           | INTB     | 0   | Interrupt request output                                                                   |  |

| 30            | RSTB     | I   | Hardware reset (active low)                                                                |  |

| 31            | GND      | S   | Ground. Connect GND pins to GND_PAD.                                                       |  |

|               | VDD_IO   | S   | I/O supply voltage, 1.8 to 3.3 ∨                                                           |  |

| 32            |          |     |                                                                                            |  |

Table 1: Pin functions

## **3. AUDIO AMPLIFIER STAGES**

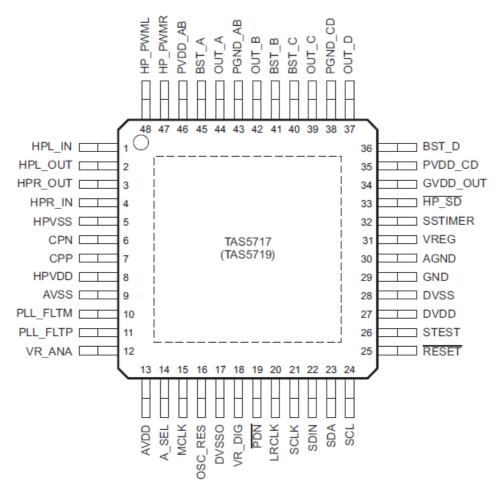

#### A. MAIN AMPLIFIER (TAS5719)(6-8 W option)

#### a. General Description

The TAS5717/TAS5719 is a 10-W/15-W, efficient, digital audio-power amplifier for driving stereo bridge-tied speakers. One serial data input allows processing of up to two discrete audio channels and seamless integration to most digital audio processors and MPEG decoders. The device accepts a wide of input data and data rates. A fully programmable data path routes these channels to the internal speaker drivers.

The TAS5717/9 is a slave-only device receiving all clocks from external sources. The TAS5717/TAS5719 operates with a PWM carrier between a 384-kHz switching rate and a 352-KHz switching rate, depending on the input sample rate. Oversampling combined with a fourth-order noise shaper provides a flat noise floor and excellent dynamic range from 20 Hz to 20 kHz.

#### b. Features

- Audio Input/Output

- TAS5717 Supports 2×10 W and TAS5719 Supports 2×15 W Output

- Wide PVDD Range, From 4.5 V to 26 V

- Efficient Class-D Operation Eliminates Need for Heatsinks

- Requires Only 3.3 V and PVDD

- One Serial Audio Input (Two Audio Channels)

- I2C Address Selection via PIN (Chip Select)

- Supports 8-kHz to 48-kHz Sample Rate (LJ/RJ/I2S)

- External Headphone-Amplifier Shutdown Signal

- Integrated CAP-Free Headphone Amplifier

- Stereo Headphone (Stereo 2-V RMS Line Driver) Outputs

- Audio/PWM Processing

- Independent Channel Volume Controls With 24-dB to Mute

- Programmable Two-Band Dynamic Range Control

- 14 Programmable Biquads for Speaker EQ

- Programmable Coefficients for DRC Filters

- DC Blocking Filters

- 0.125-dB Fine Volume Support

#### • General Features

- Serial Control Interface Operational Without MCLK

- Factory-Trimmed Internal Oscillator for Automatic Rate Detection

- Surface Mount, 48-Pin, 7-mm × 7-mm HTQFP Package

- AD, BD, and Ternary PWM-Mode Support

- Thermal and Short-Circuit Protection

- Benefits

- EQ: Speaker Equalization Improves Audio Performance

- DRC: Dynamic Range Compression. Can Be Used As Power Limiter. Enables Speaker Protection, Easy Listening, Night-Mode Listening

- DirectPath Technology: Eliminates Bulky DC Blocking Capacitors

- Stereo Headphone/Stereo Line Drivers: Adjust Gain via External Resistors, Dedicated Active Headpone Mute Pin, High Signal-to-Noise Ratio

- Two-Band DRC: Set Two Different Thresholds for Low- and High-Frequency Content

#### c. Pin descriptions and functions:

Figure 2: Pin description

| PIN      |     | TYPE <sup>(1)</sup> | 5-V      | TERMINATION <sup>(2)</sup> | DECODIDITION                                                                                                                                                                                                                             |

|----------|-----|---------------------|----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | TYPE                | TOLERANT | TERMINATION -/             | DESCRIPTION                                                                                                                                                                                                                              |

| AGND     | 30  | Р                   |          |                            | Analog ground for power stage                                                                                                                                                                                                            |

| A_SEL    | 14  | DIO                 |          |                            | This pin is monitored on the rising edge of $\overline{\text{RESET}}$ . A value of 0 makes the $I^2C$ dev address 0x54, and a value of 1 makes it 0x56.                                                                                  |

| AVDD     | 13  | Р                   |          |                            | 3.3-V analog power supply                                                                                                                                                                                                                |

| AVSS     | 9   | Р                   |          |                            | Analog 3.3-V supply ground                                                                                                                                                                                                               |

| BST_A    | 45  | Р                   |          |                            | High-side bootstrap supply for half-bridge A                                                                                                                                                                                             |

| BST_B    | 41  | Р                   |          |                            | High-side bootstrap supply for half-bridge B                                                                                                                                                                                             |

| BST_C    | 40  | Р                   |          |                            | High-side bootstrap supply for half-bridge C                                                                                                                                                                                             |

| BST_D    | 36  | Р                   |          |                            | High-side bootstrap supply for half-bridge D                                                                                                                                                                                             |

| CPN      | 6   | ю                   |          |                            | Charge-pump flying-capacitor negative connection                                                                                                                                                                                         |

| CPP      | 7   | ю                   |          |                            | Charge-pump flying-capacitor positive connection                                                                                                                                                                                         |

| DVDD     | 27  | Р                   |          |                            | 3.3-V digital power supply                                                                                                                                                                                                               |

| DVSS     | 28  | Р                   |          |                            | Digital ground                                                                                                                                                                                                                           |

| DVSSO    | 17  | Р                   |          |                            | Oscillator ground                                                                                                                                                                                                                        |

| GND      | 29  | Р                   |          |                            | Analog ground for power stage                                                                                                                                                                                                            |

| GVDD_OUT | 34  | Р                   |          |                            | Gate drive internal regulator output                                                                                                                                                                                                     |

| HPL_IN   | 1   | AI                  |          |                            | Headphone left IN (single-ended, analog IN)                                                                                                                                                                                              |

| HPL_OUT  | 2   | AO                  |          |                            | Headphone left OUT (single-ended, analog OUT)                                                                                                                                                                                            |

| HP_PWML  | 48  | DO                  |          |                            | PWM left-channel headphone out                                                                                                                                                                                                           |

| HP_PWMR  | 47  | DO                  |          |                            | PWM right-channel headphone out                                                                                                                                                                                                          |

| HPR_IN   | 4   | AI                  |          |                            | Headphone right IN (single-ended, analog IN)                                                                                                                                                                                             |

| HPR_OUT  | 3   | AO                  |          |                            | Headphone right OUT (single-ended, analog OUT)                                                                                                                                                                                           |

| HP_SD    | 33  | AI                  |          |                            | Headphone shutdown (active-low)                                                                                                                                                                                                          |

| HPVDD    | 8   | Р                   |          |                            | Headphone supply                                                                                                                                                                                                                         |

| HPVSS    | 5   | Р                   |          |                            | Headphone ground                                                                                                                                                                                                                         |

| LRCLK    | 20  | DI                  | 5-V      | Pulldown                   | Input serial audio data left/right clock (sample rate clock)                                                                                                                                                                             |

| MCLK     | 15  | DI                  | 5-V      | Pulldown                   | Master clock input                                                                                                                                                                                                                       |

| OSC_RES  | 16  | AO                  |          |                            | Oscillator trim resistor. Connect an 18-k $\Omega$ 1% resistor to DVSSO.                                                                                                                                                                 |

| OUT_A    | 44  | 0                   |          |                            | Output, half-bridge A                                                                                                                                                                                                                    |

| OUT_B    | 42  | 0                   |          |                            | Output, half-bridge B                                                                                                                                                                                                                    |

| OUT_C    | 39  | 0                   |          |                            | Output, half-bridge C                                                                                                                                                                                                                    |

| OUT_D    | 37  | 0                   |          |                            | Output, half-bridge D                                                                                                                                                                                                                    |

| PDN      | 19  | DI                  | 5-V      | Pullup                     | Power down, active-low. PDN prepares the device for loss of power<br>supplies by shutting down the noise shaper and initiating the PWM<br>stop sequence.                                                                                 |

| PGND_AB  | 43  | Р                   |          |                            | Power ground for half-bridges A and B                                                                                                                                                                                                    |

| PGND_CD  | 38  | Р                   |          |                            | Power ground for half-bridges C and D                                                                                                                                                                                                    |

| PLL_FLTM | 10  | AO                  |          |                            | PLL negative loop-filter terminal                                                                                                                                                                                                        |

| PLL_FLTP | 11  | AO                  |          |                            | PLL positive loop-filter terminal                                                                                                                                                                                                        |

| PVDD_AB  | 46  | Р                   |          |                            | Power-supply input for half-bridge output A                                                                                                                                                                                              |

| PVDD_CD  | 35  | Р                   |          |                            | Power-supply input for half-bridge output C                                                                                                                                                                                              |

| RESET    | 25  | DI                  | 5-V      | Pullup                     | Reset, active-low. A system reset is generated by applying a logic low to this pin. RESET is an asynchronous control signal that restores the DAP to its default conditions, and places the PWM in the hard-mute (high-impedance) state. |

| SCL      | 24  | DI                  | 5-V      |                            | I <sup>2</sup> C serial control clock input                                                                                                                                                                                              |

| SCLK     | 21  | DI                  | 5-V      | Pulldown                   | Serial audio data clock (shift clock). SCLK is the serial audio port input data bit clock.                                                                                                                                               |

| SDA      | 23  | DIO                 | 5-V      |                            | I <sup>2</sup> C serial control data interface input/output                                                                                                                                                                              |

| SDIN     | 22  | DI                  | 5-V      | Pulldown                   | Serial audio data input. SDIN supports three discrete (stereo) data formats.                                                                                                                                                             |

| SSTIMER  | 32  | AI                  |          |                            | Controls ramp time of OUT_X to minimize pop. Leave this pin floating<br>for BD mode. Requires capacitor of 2.2 nF to GND in AD mode. The<br>capacitor determines the ramp time.                                                          |

| STEST    | 26  | DI                  |          |                            | Factory test pin. Connect directly to DVSS.                                                                                                                                                                                              |

| VR_ANA   | 12  | Р                   |          |                            | Internally regulated 1.8-V analog supply voltage. This pin must not be used to power external devices.                                                                                                                                   |

| VR_DIG   | 18  | Р                   |          |                            | Internally regulated 1.8-V digital supply voltage. This pin must not be used to power external devices.                                                                                                                                  |

| VREG     | 31  | Р                   |          |                            | Digital regulator output. Not to be used for powering external circuitry.                                                                                                                                                                |

Table 2: Pin functions

|                               |                                      |                                                            | MIN | NOM | MAX | UNIT |

|-------------------------------|--------------------------------------|------------------------------------------------------------|-----|-----|-----|------|

|                               | Digital/analog supply voltage        | DVDD, AVDD                                                 | 3   | 3.3 | 3.6 | V    |

|                               | Half-bridge supply voltage           | PVDD_X                                                     | 4.5 |     |     | V    |

| VIH                           | High-level input voltage             | 5-V tolerant                                               | 2   |     |     | V    |

| VIL                           | Low-level input voltage              | 5-V tolerant                                               |     |     | 0.8 | V    |

| T <sub>A</sub>                | Operating ambient temperature range  |                                                            | 0   |     | 85  | °C   |

| T <sub>J</sub> <sup>(1)</sup> | Operating junction temperature range |                                                            | 0   |     | 125 | °C   |

| R <sub>L</sub> (BTL)          | Load impedance                       | Output filter: L = 15 µH, C = 680 nF                       | 4   | 8   |     | Ω    |

| L <sub>O</sub> (BTL)          | Output-filter inductance             | Minimum output inductance under<br>short-circuit condition | 4.7 |     |     | μH   |

(1) Continuous operation above the recommended junction temperature may result in reduced reliability and/or lifetime of the device.

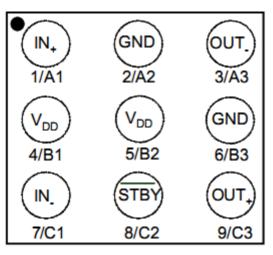

#### B. MAIN AMPLIFIER (TS4962M)(2.5 W option)

#### a. General Description

The TS4962M is a differential Class-D BTL power amplifier. It is able to drive up to 2.3W into a 4 $\Omega$  load and 1.4W into a 8 $\Omega$  load at 5V. It achieves outstanding efficiency (88%typ.) compared to classical Class-AB audio amps. The gain of the device can be controlled via two external gain-setting resistors. Pop & click reduction circuitry provides low on/off switch noise while allowing the device to start within 5ms. A standby function (active low) allows the reduction of current consumption to 10nA typ.

#### **b.** Features

- Operating from VCC = 2.4V to 5.5V

- Standby mode active low

- Output power: 3W into  $4\Omega$  and 1.75W into  $8\Omega$

- with 10% THD+N max and 5V power supply.

- Output power: 2.3W @5V or 0.75W @ 3.0V

- into  $4\Omega$  with 1% THD+N max.

- Output power: 1.4W @5V or 0.45W @ 3.0V

- into  $8\Omega$  with 1% THD+N max.

- Adjustable gain via external resistors

- Low current consumption 2mA @ 3V

- Efficiency: 88% typ.

- Signal to noise ratio: 85dB typ.

- PSRR: 63dB typ. @217Hz with 6dB gain

- PWM base frequency: 250kHz

- Low pop & click noise

- Thermal shutdown protection

- Available in flip-chip 9 x 300µm (Pb-free)

#### c. Pin descriptions and functions:

IN+: positive differential input IN-: negative differential input VDD: analog power supply GND: power supply ground STBY: standby pin (active low) OUT+: positive differential output OUT-: negative differential output

Figure 3: Pin description

| Symbol                                                         | Parameter                                                        | Value                                                             | Unit |

|----------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|------|

| V <sub>CC</sub>                                                | Supply voltage <sup>(1)</sup>                                    | 2.4 to 5.5                                                        | V    |

| V <sub>IC</sub> Common mode input voltage range <sup>(2)</sup> |                                                                  | 0.5 to V <sub>CC</sub> - 0.8                                      | V    |

| V <sub>STBY</sub>                                              | Standby voltage input: <sup>(3)</sup><br>Device ON<br>Device OFF | $1.4 \le V_{STBY} \le V_{CC}$<br>GND $\le V_{STBY} \le 0.4^{(4)}$ | V    |

| R <sub>L</sub>                                                 | Load resistor                                                    | ≥ 4                                                               | Ω    |

| R <sub>thja</sub>                                              | Thermal resistance junction to ambient <sup>(5)</sup>            | 90                                                                | °C/W |

1. For V<sub>CC</sub> from 2.4V to 2.5V, the operating temperature range is reduced to  $0^{\circ}C \leq T_{amb} \leq 70^{\circ}C$ .

2. For V\_{CC} from 2.4V to 2.5V, the common mode input range must be set at V\_{CC}/2.

3. Without any signal on  $V_{\mbox{\scriptsize STBY}},$  the device will be in standby.

4. Minimum current consumption is obtained when V<sub>STBY</sub> = GND.

5. With heat sink surface = 125 mm<sup>2</sup>.

#### Table 4: Recommended operating conditions

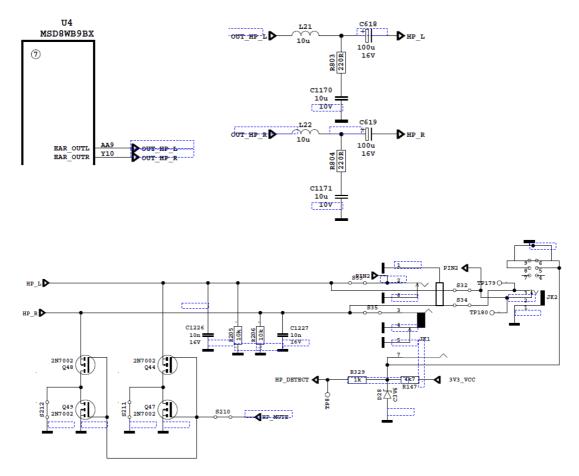

#### C. HEADPHONE AMPLIFIER STAGE

Headphone is a SoC (single on chip) configuration in mainboard, design scheme is shown in figure 4.

Figure 4: Headphone

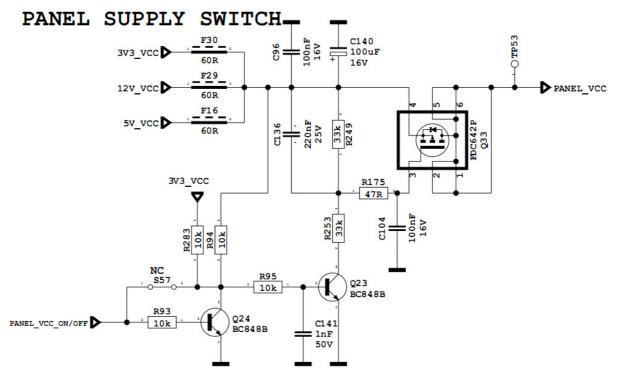

## 4. POWER STAGE

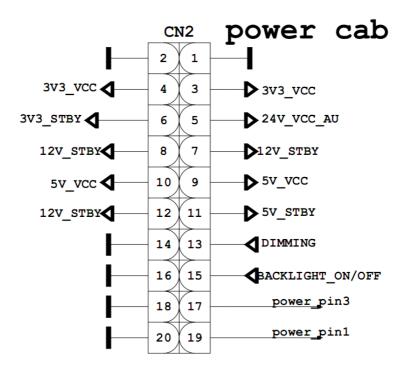

Figure 5: Power socket and power options

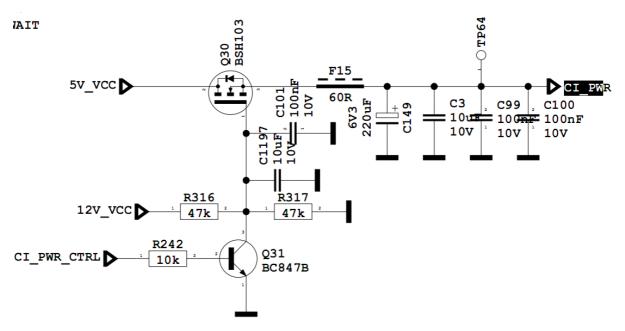

Power socket is used for taking voltages which are 3.3V, 12V, 5V and 24V(VDD\_Audio). These voltages are produced in power card. Also socket is used for giving dimming, backlight and standbye signals with power card. It is shown in figure 5.

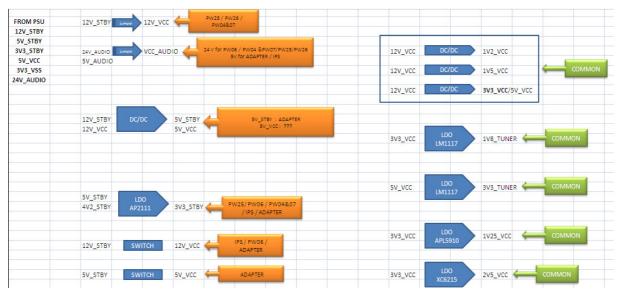

24V(VDD\_Audio) goes directly to the audio side, through power socket other incoming voltages from power card are converted several voltages.

Figure 6: Power steps

#### **FDC642P**

#### **General Description and Features**

# Single P-Channel 2.5V Specified PowerTrench $^{\textcircled{B}}$ MOSFET -20 V, -4.0 A, 65 m $\Omega$

#### Features

- Max r<sub>DS(on)</sub> = 65 mΩ at V<sub>GS</sub> = -4.5 V, I<sub>D</sub> = -4.0 A

- Max r<sub>DS(on)</sub> = 100 mΩ at V<sub>GS</sub> = -2.5 V, I<sub>D</sub> = -3.2 A

- Fast switching speed

- Low gate charge (11nC typical)

- High performance trench technology for extremely low r<sub>DS(on)</sub>

SuperSOT<sup>TM</sup>-6 package: small footprint (72% smaller than standard SO-8); low profile (1 mm thick)

- Termination is Lead-free and RoHS Compliant

#### **General Description**

This P-Channel 2.5V specified MOSFET is produced using Fairchild's advanced PowerTrench® process that has been especially tailored to minimize on-state resistance and yet maintain low gate charge for superior switching performance.

These devices have been designed to offer exceptional power dissipation in a very small footprint for applications where the larger packages are impractical.

#### Applications

- Load switch

- Battery protection

- Power management

#### **TPS65251**

#### a) General Description

The TPS65251 features three synchronous wide input range high efficiency buck converters. The converters are designed to simplify its application while giving the designer the option to optimize their usage according to the target application.

The converters can operate in 5-, 9-, 12- or 15-V systems and have integrated power transistors. The output voltage can be set externally using a resistor divider to any value between 0.8 V and close to the input supply. Each converter features enable pin that allows a delayed start-up for sequencing purposes, soft start pin that allows adjustable soft-start time by choosing the soft-start capacitor, and a current limit (RLIMx) pin that enables designer to adjust current limit by selecting an external resistor and optimize the choice of inductor. The current mode control allows a simple RC compensation.

The switching frequency of the converters can either be set with an external resistor connected to ROSC pin or can be synchronized to an external clock connected to SYNC pin if needed. The switching regulators are designed to operate from 300 kHz to 2.2 MHz. 180° out of phase operation between Buck 1 and Buck 2, 3 (Buck 2 and 3 run in phase) minimizes the input filter requirements.

TPS65251 features a supervisor circuit that monitors each converter output. The PGOOD pin is asserted once sequencing is done, all PG signals are reported and a selectable end of reset time lapses. The polarity of the PGOOD signal is active high.

TPS65251 also features a light load pulse skipping mode (PSM) by allowing the LOW\_P pin tied to V3V. The PSM mode allows for a reduction on the input power supplied to the system when the host processor is in stand-by (low activity) mode.

#### b) Features

- Wide Input Supply Voltage Range (4.5 V 18 V)

- 0.8 V, 1% Accuracy Reference

- Continuous Loading: 3 A (Buck 1), 2 A (Buck 2 and 3)

- Maximum Current: 3.5 A (Buck 1), 2.5 A (Buck 2 and 3)

- Adjustable Switching Frequency 300 kHz 2.2 MHz Set By External Resistor

- Dedicated Enable for Each Buck

- External Synchronization Pin for Oscillator

- External Enable/Sequencing and Soft Start Pins

- Adjustable Current Limit Set By External Resistor

- Soft Start Pins

- Current-Mode Control With Simple Compensation Circuit

- Power Good

- Optional Low Power Mode Operation for Light Loads

- QFN Package, 40-Pin 6 mm x 6 mm RHA

#### APPLICATIONS

- Set Top Boxes

- Blu-ray DVD

- Security Camera

- Car Audio/Video

- DTV

- DVR

over operating free-air temperature range (unless otherwise noted)

|     |                         | MIN | NOM MAX | UNIT |

|-----|-------------------------|-----|---------|------|

| VIN | Input operating voltage | 4.5 | 18      | V    |

| TJ  | Junction temperature    | -40 | 125     | °C   |

Table 5: Recommended operating conditions

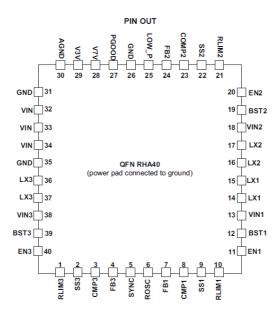

#### Figure 7: Pin description

| NAME  | NO.    | I/O   | DESCRIPTION                                                                                                                                                                                                                          |  |

|-------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RLIM3 | 1      | I     | Current limit setting for Buck 3. Fit a resistor from this pin to ground to set the peak current limit on the output inductor.                                                                                                       |  |

| SS3   | 2      | I     | Soft start pin for Buck 3. Fit a small ceramic capacitor to this pin to set the converter soft start time.                                                                                                                           |  |

| COMP3 | 3      | 0     | Compensation for Buck 3. Fit a series RC circuit to this pin to complete<br>the compensation circuit of this converter.                                                                                                              |  |

| FB3   | 4      | I     | Feedback input for Buck 3. Connect a divider set to 0.8V from the output<br>of the converter to ground.                                                                                                                              |  |

| SYNC  | 5      | I     | Synchronous clock input. If there is a sync clock in the system, connect to the pin. When not used connect to GND.                                                                                                                   |  |

| ROSC  | 6      | I     | Oscillator set. This resistor sets the frequency of internal autonomous<br>clock. If external synchronization is used resistor should be fitted and set<br>to ~70% of external clock frequency.                                      |  |

| FB1   | 7      | I     | Feedback pin for Buck 1. Connect a divider set to 0.8 V from the outp<br>the converter to ground.                                                                                                                                    |  |

| COMP1 | 8      | 0     | Compensation pin for Buck 1. Fit a series RC circuit to this pin to<br>complete the compensation circuit of this converter.                                                                                                          |  |

| SS1   | 9      | I     | Soft start pin for Buck 1. Fit a small ceramic capacitor to this pin to set the converter soft start time.                                                                                                                           |  |

| RLIM1 | 10     | I     | Current limit setting pin for Buck 1. Fit a resistor from this pin to ground to set the peak current limit on the output inductor.                                                                                                   |  |

| EN1   | 11     | I     | Enable pin for Buck 1. A low level signal on this pin disables it. If pin is left open a weak internal pull-up to V3V will allow for automatic enable. For a delayed start-up add a small ceramic capacitor from this pin to ground. |  |

| BST1  | 12     | I     | Bootstrap capacitor for Buck 1. Fit a 47-nF ceramic capacitor from this pin<br>to the switching node.                                                                                                                                |  |

| VIN1  | 13     | L. L. | Input supply for Buck 1. Fit a 10-µF ceramic capacitor close to this pin.                                                                                                                                                            |  |

| LX1   | 14, 15 | 0     | Switching node for Buck 1                                                                                                                                                                                                            |  |

| LX2   | 16, 17 | 0     | Switching node for Buck 2                                                                                                                                                                                                            |  |

| VIN2  | 18     | L. L. | Input supply for Buck 2. Fit a 10-µF ceramic capacitor close to this pin.                                                                                                                                                            |  |

| BST2  | 19     | I     | Bootstrap capacitor for Buck 2. Fit a 47-nF ceramic capacitor from this pin to the switching node.                                                                                                                                   |  |

| EN2   | 20     | I   | Enable pin for Buck 2. A low level signal on this pin disables it. If pin is left open a weak internal pull-up to V3V will allow for automatic enable. For a delayed start-up add a small ceramic capacitor from this pin to ground. |  |

|-------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RLIM2 | 21     | I   | Current limit setting for Buck 2. Fit a resistor from this pin to ground to set<br>the peak current limit on the output inductor.                                                                                                    |  |

| SS2   | 22     | I   | Soft start pin for Buck 2. Fit a small ceramic capacitor to this pin to set the<br>converter soft start time.                                                                                                                        |  |

| COMP2 | 23     | 0   | Compensation pin for Buck 2. Fit a series RC circuit to this pin to<br>complete the compensation circuit of this converter                                                                                                           |  |

| FB2   | 24     | I   | Feedback input for Buck 2. Connect a divider set to 0.8 V from the output<br>of the converter to ground.                                                                                                                             |  |

| LOW_P | 25     | L L | Low power operation mode(active high) input for TPS65251                                                                                                                                                                             |  |

| GND   | 26     |     | Ground pin                                                                                                                                                                                                                           |  |

| PGOOD | 27     | 0   | Power good. Open drain output asserted after all converters are<br>sequenced and within regulation. Polarity is factory selectable (active<br>default).                                                                              |  |

| V7V   | 28     | 0   | Internal supply. Connect a 10-µF ceramic capacitor from this pin to ground.                                                                                                                                                          |  |

| V3V   | 29     | 0   | Internal supply. Connect a 10-µF ceramic capacitor from this pin to<br>ground.                                                                                                                                                       |  |

| AGND  | 30     |     | Analog ground. Connect all GND pins and the power pad together.                                                                                                                                                                      |  |

| GND   | 31     |     | Ground pin                                                                                                                                                                                                                           |  |

| VIN   | 32     |     | Input supply                                                                                                                                                                                                                         |  |

| VIN   | 33     | 1   | Input supply                                                                                                                                                                                                                         |  |

| VIN   | 34     | 1   | Input supply                                                                                                                                                                                                                         |  |

| GND   | 35     |     | Ground pin                                                                                                                                                                                                                           |  |

| LX3   | 36, 37 | 0   | Switching node for Buck 3                                                                                                                                                                                                            |  |

| VIN3  | 38     |     | Input supply for Buck 3. Fit a 10-µF ceramic capacitor close to this pin.                                                                                                                                                            |  |

| BST3  | 39     | I.  | Bootstrap capacitor for Buck 3. Fit a 47-nF ceramic capacitor from this pin to the switching node.                                                                                                                                   |  |

| EN3   | 40     | I   | Enable pin for Buck 3. A low level signal on this pin disables it. If pin is left open a weak internal pull-up to V3V will allow for automatic enable. For a delayed start-up add a small ceramic capacitor from this pin to ground. |  |

| PAD   |        |     | Power pad. Connect to ground.                                                                                                                                                                                                        |  |

|       |        |     |                                                                                                                                                                                                                                      |  |

#### **Table 6: Pin functions**

#### <u>MP1484</u>

#### a) General Description

The MP1484 is a monolithic synchronous buck regulator. The device integrates top and bottom  $85m\Omega$  MOSFETS that provide 3A of continuous load current over a wide operating input voltage of 4.75V to 18V. Current mode control provides fast transient response and cycle-by-cycle current limit.

An adjustable soft-start prevents inrush current at turn-on and in shutdown mode, the supply current drops below  $1\mu A$ .

The MP1484 is PIN compatible to the MP1482 2A/18V/Synchronous Step-Down Converter.

#### **b)** Features

- 3A Continuous Output Current

- Wide 4.75V to 18V Operating Input Range

- Integrated 85mΩ Power MOSFET Switches

- Output Adjustable from 0.925V to 20V

- Up to 95% Efficiency

- Programmable Soft-Start

- Stable with Low ESR Ceramic Output Capacitors

- Fixed 340KHz Frequency

- Cycle-by-Cycle Over Current Protection

- Input Under Voltage Lockout

- Thermally Enhanced 8-Pin SOIC Package

#### APPLICATIONS

- FPGA, ASIC, DSP Power Supplies

- LCD TV

- Green Electronics/Appliances

- Notebook Computers

#### PACKAGE REFERENCE

\* For Tape & Reel, add suffix –Z (e.g. MP1484EN -Z) For Lead Free, add suffix –LF (e.g. MP1484EN - LF-Z)

# ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage VIN                                                                                   | –0.3V to +24V                    |

|------------------------------------------------------------------------------------------------------|----------------------------------|

|                                                                                                      | –1V to V <sub>IN</sub> + 0.3V    |

| Boost Voltage V <sub>BS</sub>                                                                        | $V_{SW} - 0.3V$ to $V_{SW} + 6V$ |

| All Other Pins                                                                                       | –0.3V to +6V                     |

| Junction Temperature                                                                                 |                                  |

| Lead Temperature                                                                                     |                                  |

| Storage Temperature                                                                                  | 65°C to +150°C                   |

| Recommended Oper                                                                                     | rating Conditions <sup>(2)</sup> |

| Input Voltage VIN                                                                                    | 4.75V to 18V                     |

| Output Voltage VOUT                                                                                  |                                  |

| Ambient Operating Temp                                                                               | –20°C to +85°C                   |

| Thermal Resistance                                                                                   |                                  |

| SOIC8N(Exposed Pad)                                                                                  | 50 10 °C/W                       |

| Notes:<br>1) Exceeding these ratings may<br>2) The device is not guaranteed<br>operating conditions. |                                  |

Measured on approximately 1" square of 1 oz copper.

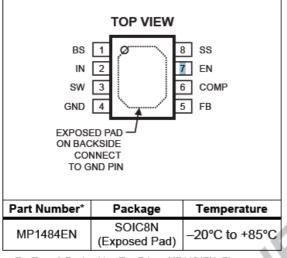

Figure 8: General description

| Pin # | Name | Description                                                                                                                                                                                                                                       |  |  |  |  |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1     | BS   | High-Side Gate Drive Boost Input. BS supplies the drive for the high-side N-Channel MOSFET switch. Connect a $0.01\mu$ F or greater capacitor from SW to BS to power the high side switch.                                                        |  |  |  |  |

| 2     | IN   | r Input. IN supplies the power to the IC, as well as the step-down converter switches.<br>IN with a 4.75V to 18V power source. See <i>Input Capacitor</i> .                                                                                       |  |  |  |  |

| 3     | SW   | Power Switching Output. SW is the switching node that supplies power to the output. Connect the output LC filter from SW to the output load. Note that a capacitor is required from SW to BS to power the high-side switch.                       |  |  |  |  |

| 4     | GND  | Ground (Connect the exposed pad to Pin 4).                                                                                                                                                                                                        |  |  |  |  |

| 5     | FB   | Feedback Input. FB senses the output voltage and regulates it. Drive FB with a resistive voltage divider connected to it from the output voltage. The feedback threshold is 0.925V. See <i>Setting the Output Voltage</i> .                       |  |  |  |  |

| 6     | COMP | Compensation Node. COMP is used to compensate the regulation control loop. Connect a series RC network from COMP to GND. In some cases, an additional capacitor from COMP to GND is required. See <i>Compensation Components</i> .                |  |  |  |  |

| 7     | EN   | Enable Input. EN is a digital input that turns the regulator on or off. Drive EN high to turn on the regulator; low to turn it off. Attach to IN with a $100k\Omega$ pull up resistor for automatic startup.                                      |  |  |  |  |

| 8     | SS   | Soft-Start Control Input. SS controls the soft-start period. Connect a capacitor from SS to GND to set the soft-start period. A $0.1\mu$ F capacitor sets the soft-start period to 15ms. To disable the soft-start feature, leave SS unconnected. |  |  |  |  |

**Table 7: Pin functions**

#### APL5910

#### a) General Description

The APL5910 is a 1A ultra low dropout linear regulator. The IC needs two supply voltages, one is a control voltage (VCNTL) for the control circuitry, the other is a main supply voltage (VIN) for power conversion, to reduce power dissipation and provide extremely low dropout voltage. The APL5910 integrates many functions. A Power-On- Reset (POR) circuit monitors both supply voltages on VCNTL and VIN pins to prevent erroneous operations. The functions of thermal shutdown and current-limit protect the device against thermal and current over-loads. A POK indicates that the output voltage status with a delay time set internally. It can control other converter for power sequence. The APL5910 can be enabled by other power systems. Pulling and holding the EN voltage below 0.4V shuts off the output.

The APL5910 is available in a SOP-8P package which features small size as SOP-8 and an Exposed Pad to reduce the junction-to-case resistance to extend power range of applications.

#### b) Features

- Ultra Low Dropout

- 0.12V (Typical) at 1AOutput Current

- 0.8V Reference Voltage

- High Output Accuracy

- ±1.5% over Line, Load, and Temperature Range

- Fast Transient Response

- Adjustable Output Voltage

- Power-On-Reset Monitoring on Both VCNTL and VIN Pins

- Internal Soft-Start

- Current-Limit and ShortCurrent-Limit Protections

- Thermal Shutdown with Hysteresis

- Open-Drain VOUT Voltage Indicator (POK)

- Low Shutdown Quiescent Current (< 30mA)

- Shutdown/Enable Control Function

- Simple SOP-8P Package with Exposed Pad

- Lead Free and Green Devices Available (RoHS Compliant)

#### APPLICATIONS

- Motherboards, VGA Cards

- Notebook PCs

- Add-in Cards

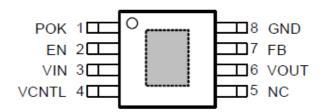

#### **Figure 9: Pin configuration**

| Symbol              | P                           | Range                                                                | Unit      |    |

|---------------------|-----------------------------|----------------------------------------------------------------------|-----------|----|

| V <sub>CNTL</sub>   | VCNTL Supply Voltage        | 3.0 ~ 5.5                                                            | V         |    |

| VIN                 | VIN Supply Voltage          |                                                                      | 1.0 ~ 5.5 | V  |

| Vout                | VOUT Output Voltage (when V | 0.8 ~ V <sub>IN</sub> - V <sub>DROP</sub>                            | V         |    |

| Ι <sub>ουτ</sub>    | VOUT Output Current         | 0~1                                                                  | А         |    |

| R2                  | FB to GND                   | FB to GND                                                            |           | Ω  |

|                     | VOUT Output Capacitance     | I <sub>OUT</sub> =1A at 25% nominal V <sub>OUT</sub>                 | 8 ~ 600   | μF |

| COUT                |                             | I <sub>OUT</sub> =0.5A at 25% nominal V <sub>OUT</sub>               | 8 ~ 900   |    |

|                     |                             | $I_{\text{OUT}}\text{=}0.25\text{A}$ at 25% nominal $V_{\text{OUT}}$ | 8 ~ 1100  |    |

| ESR <sub>COUT</sub> | ESR of VOUT Output Capacito | r                                                                    | 0 ~ 200   | mΩ |

| TA                  | Ambient Temperature         |                                                                      | -40 ~ 85  | °C |

| TJ                  | Junction Temperature        |                                                                      | -40 ~ 125 | °C |

**Table 8: Recommended operating conditions**

| PIN |       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME  | Fore tion                                                                                                                                                                                                                                                                                                                                                                                      |

| 1   | POK   | Power-OK signal output pin. This pin is an open-drain output used to indicate the status of output<br>voltage by sensing FB voltage. This pin is pulled low when output voltage is not within the<br>Power-OK voltage window.                                                                                                                                                                  |

| 2   | EN    | Active-high enable control pin. Applying and holding the voltage on this pin below the enable voltage threshold shuts down the output. When re-enabled, the IC undergoes a new soft-start process. When left this pin open, an internal pull-up current (5μA typical) pulls the EN voltage and enables the regulator.                                                                          |

| 3   | VIN   | Main supply input pin for voltage conversions. A decoupling capacitor (≥10µF recommended) is<br>usually connected near this pin to filter the voltage noise and improve transient response. The<br>voltage on this pin is monitored for Power-On-Reset purpose                                                                                                                                 |

| 4   | VCNTL | Bias voltage input pin for internal control circuitry. Connect this pin to a voltage source (+5V recommended). A decoupling capacitor (1µF typical) is usually connected near this pin to filter the voltage noise. The voltage at this pin is monitored for Power-On-Reset purpose.                                                                                                           |

| 5   | NC    | No Connection.                                                                                                                                                                                                                                                                                                                                                                                 |

| 6   | VOUT  | Output pin of the regulator. Connecting this pin to load and output capacitors ( $10\mu$ F at least) is required for stability and improving transient response. The output voltage is programmed by the resistor-divider connected to FB pin. The VOUT can provide 1A (max.) load current to loads. During shutdown, the output voltage is quickly discharged by an internal pull-low MOSFET. |

| 7   | FB    | Voltage Feedback Pin. Connecting this pin to an external resistor divider receives the feedback voltage of the regulator.                                                                                                                                                                                                                                                                      |

#### **Table 9: Pin description**

#### LM1117

#### a) General Description

The LM1117 is a series of low dropout voltage regulators with a dropout of 1.2V at 800mA of load current. It has the same pin-out as National Semiconductor's industry standard LM317.

The LM1117 is available in an adjustable version, which can set the output voltage from 1.25V to 13.8V with only two external resistors. In addition, it is also available in five fixed voltages, 1.8V, 2.5V, 2.85V, 3.3V, and 5V.

The LM1117 offers current limiting and thermal shutdown. Its circuit includes a zener trimmed bandgap reference to assure output voltage accuracy to within  $\pm 1\%$ .

The LM1117 series is available in LLP, TO-263, SOT-223, TO-220, and TO-252 D-PAK packages. A minimum of  $10\mu$ F tantalum capacitor is required at the output to improve the transient response and stability.

#### b) Features

- Available in 1.8V, 2.5V, 2.85V, 3.3V, 5V, and Adjustable Versions

- Space Saving SOT-223 and LLP Packages

- Current Limiting and Thermal Protection

- Output Current 800mA

- Line Regulation 0.2% (Max)

- Load Regulation 0.4% (Max)

- Temperature Range:

- LM1117 0°C to 125°C

- LM1117I –40°C to 125°C

- Applications

- 2.85V Model for SCSI-2 Active Termination

- Post Regulator for Switching DC/DC Converter

- High Efficiency Linear Regulators

- Battery Charger

- Battery Powered Instrumentation

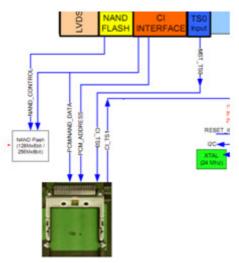

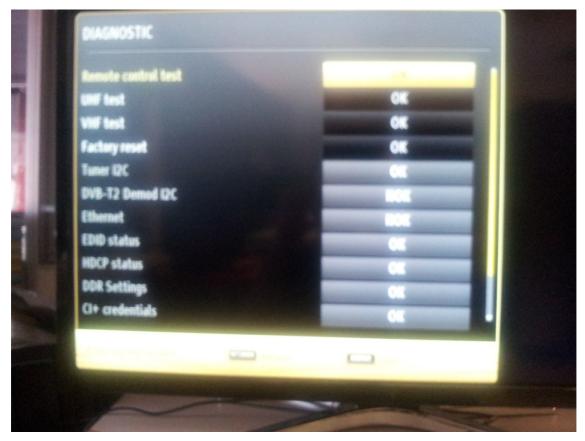

# 5. MICROCONTROLLER (MSTAR MSD8WB9BX)

#### a) General Description

The MSD8WB9BX is MStar's most up-to-date system-on-chip flagship for flat panel integrated digital television products. Building on the success of MStar's current solutions, the MSD8WB9BX hosts the most advanced picture processing engine, *MStarACE<sup>PRO</sup>*, for all the *Experts* in various fields of TV video quality tuning to develop the state-of-the-art TV and DTV system.

*MStarACE*<sup>PRO</sup>, the Professional Edition of MStar color processor, includes all MStar's successful color-tuning tools and a newly added multi-dimensional color/sharpening/NR formula that can quickly reflect subtle or sudden changes in even darker, brighter or mixture scenes. With this ultimate color processor, a specially designed color remapping system for modern wider gamut displays and an easy-to-use color-tool UI, developers can quickly and easily identify PQ characteristic from the most high-end panel models to the most conventional panel models.

The MSD8WB9BX integrates DTV/multi-media all-purpose AV decoder, DVB-T/DVB-C demodulator, VIF demodulator and Sound/Video processor into a single device. This allows the overall BOM to be reduced significantly making the MSD8WB9BX a very cost effective multi-media DTV solution.

The MSD8WB9BX enables feature rich products that bring differentiation to the iDTV market. By the use of AV decoder capable of decoding a plethora of high definition content with Ethernet, USB 2.0 connectivity and a powerful CPU/GPU, an MSD8WB9BX based system can provide a high quality networking application and media-center experience.

For standard users, the MSD8WB9BX provides multi-standard analog TV support with adaptive 3D video decoding and VBI data extraction. The build-in audio decoder is capable of decoding FM, AM, NICAM, A2, BTSC and EIA-J sound standards. The MSD8WB9BX supplies all the necessary A/V inputs and outputs to complete a receiver design including a multi-port HDMI receiver and component video ADC. All input selection multiplexed for video and audio are integrated, including full SCART support with CVBS output.

To meet the increasingly popular energy legislative requirements without the use of additional hardware, the MSD8WB9BX has an ultra low power standby mode during which an embedded MCU can act upon standby events and wake up the system as required.

#### b) Features

MSD8WB9BX, a single chip iDTV solution that supports channel decoding, MPEG decoding, and media-center functionality enabled by a high performance AV CODEC and CPU Key features includes,

- 1. DVB-T/C Front-End Demodulator

- 2. A Multi-Standard A/V Format Decoder

- 3. The MACE<sup>PRO</sup> Video Processor

- 4. Home Theater Sound Processor

- 5. Internet and Variety of Connectivity Support

- 6. Dual-stream decoder for 3D contents

- 7. Multi-Purpose CPU for OS and Multimedia

- 8. Peripheral and Power Management

- High Performance Micro-processor

- Ultra high speed/performance 32-bit RISC CPU

- Memory Management Unit for Linux support

- Three full duplex UARTs

- Supports USB and ISP programming

- DMA Engine

- Transport Stream De-multiplexer

- Supports two parallel TS interfaces, with or without sync signal

- Supports TS input and output for external CI module

- Supports external demodulator of ISDB, DTMB, or DVB-T2/S2

- Maximum TS data rate is 16 MB/sec

- 32 general purpose PID filters and section filters for each transport stream de-multiplexer

- Supports additional audio/video/PCR filters

- Supports TS DMA channel for time-shifting PVR

- Supports 3DES/DES and AES encryption/decryption

#### MPEG-2 Video Decoder

- ISO/IEC 13818-2 MPEG-2 video MP@HL

- Automatic frame rate conversion

- Supports resolution up to HDTV (1080i, 720p) and SDTV

- MPEG-4 Video Decoder

- ISO/IEC 14496-2 MPEG-4 ASP video decoding

- Supports resolutions up to HDTV

- (1080p@30fps)

- Supports DivX<sup>1</sup> Home Theater & HD profiles Optional & Plus HD Optional

- Supports VC-1 Optional, FLV video format

- decoding

- H.264 Decoder

- ITU-T H.264, ISO/IEC 14496-10 video decoding (Main and high profile up to level 4.1), MVC video decoding

- Supports dual-stream decoding

- Supports resolutions for all DVB, ATSC, HDTV, DVD and VCD

- Supports resolution up to 1080p@50fps

- Supports CABAC and CAVLC stream types

- Processing of ES and PES streams, extraction and provision of time stamps

- Up to 40 Mbits bitrate (Blu-ray spec.)

- AVS Decoder Optional

- Supports Jizhun profile, level 6.0

- Supports resolution up to 1920x1088 @30fps

- Supports bit-rate up to 20Mbps

- Supports dual-stream decoding for 3D contents

- RealMedia Decoder<sup>Optional</sup>

- Supports maximum resolution up to 1080p@30fps

- Supports RV8, RV9, RV10, RA8-LBR and HE-AAC decoders

- Supports file formats with RM and RMVB

- Supports Picture Re-sampling

- Supports in-loop de-block for B-frame

#### Hardware JPEG

- Supports sequential mode, single scan

- Supports both color and grayscale pictures

- Following the file header scan the hardware decoder fully handles the decode process

- Supports programmable Region of Interest (ROI)

- Supports formats: 422/411/420/444/422T

- Supports scaling down ratios: 1/2, 1/4, 1/8

- Supports picture rotation

- NTSC/PAL/SECAM Video Decoder

- Supports NTSC-M, NTSC-J, NTSC-4,43, PAL (B, D, G, H, M, N, I, Nc), and SECAM standards

- Automatic standard detection

- Motion adaptive 3D comb filter

- Four configurable CVBS & Y/C S-video inputs

- Supports Teletext, Closed Caption (analog CC 608/ analog CC 708/digital CC 608/digital CC 708), V-chip and SCTE

- Multi-Standard TV Sound Processor

- SIF audio decoding

- Supports BTSC/A2/EIA-J demodulation

- Supports NICAM/FM/AM demodulation

- Supports MTS Mode Mono/Stereo/SAP in BTSC/ EIA-J mode

- Supports Mono/Stereo/Dual in A2/NICAM mode

Automatic color calibration

- Built-in audio sampling rate conversion (SRC)

Analogue RGB Auto-Configuration & Detection

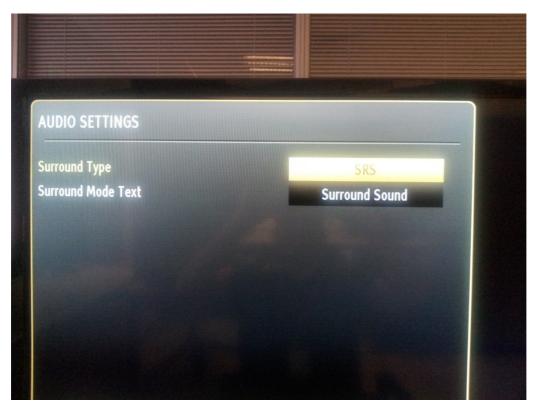

- Audio processing for loudspeaker channel, including volume, balance, mute, tone, EQ, virtual stereo/surround and treble/bass controls

- Advanced sound processing options available, for example: Dolby<sup>1</sup>, SRS<sup>2</sup>, BBE<sup>3</sup>, QSound<sup>4</sup>, Audyssey<sup>5</sup>

- Supports digital audio format decoding:

- MPEG-1, MPEG-2 (Layer I/II), MP3, Dolby Digital (AC-3) Optional, AAC-LC, HE-AAC, WMA, and WMA9 Pro

- Supports<sup>Optional</sup> Dolby Digital Plus, Dolby

Trademark of Dolby Laboratories

- Trademark of SRS Labs, Inc.

- Registered trademark of BBE Sound, Inc.

- Registered trademark of QSound Labs, Inc.

- Registered trademark of Audyssey Laboratories, Inc. Optional Please see Ordering Guide for details.

Optional Please see Ordering Guide for details.

Pulse, and MS10 multistream decoder, including Dolby Digital Encoder for transcoding streams to Dolby Digital 5.1 (DDCO)

- · Supports MPEG Audio, Dolby Digital, Dolby Digital Plus, HE-AAC format AD (Audio Description)

- Supports MPEG audio encoding Supports time-shifting PVR

- Audio Interface

- · One SIF audio input interface with minimal external saw filters

- Six L/R audio line-inputs

- Three L/R outputs for main speakers and additional TV line-outputs

- One embedded stereo headphone driver

- I2S digital audio output

- S/PDIF digital audio output & input

- HDMI<sup>6</sup> audio channel processing

- Programmable delay for audio/video synchronization

- Analog RGB Compliant Input Ports

- Three analog ports support up to 1080P

- Supports PC RGB input up to SXGA@75Hz

- Supports HDTV RGB/YPbPr/YCbCr

- Supports Composite Sync and SOG Sync-on-Green

- Auto input signal format and mode detection

- · Auto-tuning function including phasing,

- positioning, offset, gain, and jitter detection Sync Detection for H/V Sync

- DVI/HDCP/HDMI Compliant Input Ports

- Four HDMI/DVI Input ports

- HDMI 1.3/1.4 Compliant

- MStar iSwitch for fast HDMI switching

- HDCP 1.1/1.3 Compliant

- 225MHz @ 1080P 60Hz input with 12-bit Deep-color support

- Supports HDMI CEC

- Supports HDMI 1.4a 3D format input

- Supports HDMI 4Kx2K input

- Supports HDMI ARC

- Single link DVI 1.0 compliant

<sup>6</sup> Registered trademark of HDMI Licensing LLC

- Robust receiver with excellent long-cable support

- MStar Advanced Color Engine Professional Edition (MStarACE<sup>PRO</sup>)

- 10/12-bit internal data processing

- · High taps and fully programmable

- multi-function scaling engine

- Nonlinear video scaling supports various modes including Panorama

- Supports dynamic scaling for RM, VC-1<sup>Optiona</sup>

- High-Quality DTV video processor

- 3D motion video deinterlacer with motion object stabilizer

- Edge-oriented deinterlacer with edge and artifact smoother

- Automatic 3:2/2:2/M:N pull-down detection and recovery

- 3D multi-purpose noise reduction for DTV or lousy air/cable input

- MPEG artifact removal including de-blocking

- and mosquito noise reduction - Arbitrary frame rate conversion

- Automatic picture enhancement:

- Includes all features in MACE-3/4 engine

- 3D adaptive color control enabling vivid visual reception in the true world from most dark to most bright scenes

- 3D adaptive sharpening control enabling crystal clear visual reception without distorting scene reality

- Supports sRGB and xvYCC color processing

- Supports HDMI 1.3 deep color format

- Supports enhanced and seamless color mapping for wider gamut panels

- Programmable 12-bit RGB gamma CLUT

- Supports 2D to 3D conversion

#### DVB-T/DVB-C Demodulator

- Digital carrier frequency offset correction: +500KHz

- Optimised for SFN channels with pre/post-cursive echoes inside/outside the guard

- Acquisition range ±857kHz includes up to 3x ±1/6 MHz transmitter offset

- Meets Nordig Unified 1.0.3, D-Book 5.0, EICTA E-Book/C-Book test requirement

- ITU J.83 Annex A/C, DVB-C (EN 300 429) compliant

- Supports DVB-C 0.7-7M Baud symbol rate

- ±400kHz internal carrier offset recovery range

- · 6.8 usecs echo cancellation at 7 Msym/s

- Supports IF, low-IF inputs

- Ultra-fast automatic blind UHF/VHF channel scan (constellations and symbol rate)

# Flattronit

#### Output Interface

- Single/dual link 8/10-bit LVDS output Supports panel resolution up to Full-HD

- (1920x1080) @ 60Hz

- Supports dithering options

- Spread spectrum output frequency for EMI suppression

- CVBS Video Encode

- · Supports all NTSC/PAL TV Standard

- Stand-alone scaling engine

- Programmable Hue, Contract, Brightness

- Supports TTX/CC/WSS output

- **CVBS Video Outputs**

- Allows CVBS output from CVBS video encoder

- Supports CVBS bypass output

- 3D-like Graphics Engine

- Hardware Graphics Engine for responsive interactive applications

- · Supports point draw, line draw, rectangle draw/fill, text draw and trapezoid draw

- BitBlt, stretch BitBlt, trapezoid BitBlt, mirror BitBlt and rotate BitBlt

- Supports alpha and destination alpha compare

- Raster Operation (ROP)

- Supports Porter-Duff VIF Demodulator

- Compliant with NTSC M/N, PAL B, G/H, I, D/K, SECAM L/L' standards

- Digital low IF architecture

- Audio/Video dual-path processor

- Stepped-gain PGA with 25 dB tuning range and

- 1 dB tuning resolution

- Maximum IF gain of 37 dB

- Programmable TOP to accommodate different tuner gain and SAW filter insertion loss to optimize noise and linearity performance

- Multi-standard processing with single SAW

- Supports silicon tuner low IF output architecture

#### Connectivity

- Two USB 2.0 host ports

- USB architecture designed for efficient support of external storage devices in conjunction with off air broadcasting

- Built-in 10/100Mbps Ethernet PHY and MAC

- · MStar proprietary I/F for Wi-Fi and Bluetooth companion chips

- Miscellaneous

- · DRAM interface supporting up to two 16-bit DDR3 @ 1.6GHz

- Supports RTC

- Supports Common Interface for conditional access support

- · Bootable SPI interface with serial flash support

- Parallel interface for NAND flash support

- Power control module with ultra low power