# 8-BIT SINGLE CHIP MICROCONTROLLER LC86F3548A

# LC86F3548A

8-bit Single Chip Microcontroller with on-chip 64K-byte Flash Memory (ROM 48K -byte + CGROM 16K-byte), on-chip 640-byte RAM and 176 × 9 bit OSD RAM

### Overview

The LC86F3548A is a CMOS 8-bit single chip microcontroller with flash memory for the LC863500 series. This microcontroller contains the following on-chip functional blocks:

- CPU : Operable at a minimum bus cycle time of  $0.424\mu$ s

- On-chip ROM capacity : 64K bytes Flash Memory

Program ROM : 48K bytes CGROM : 16K bytes

- On-chip RAM capacity : 640 bytes

- OSD RAM :  $176 \times 9$  bits

- On-screen display controller

- Four channels  $\times$  6-bit AD Converter

- Three channels  $\times$  7-bit PWM

- Two 16-bit timer/counters, 14-bit base timer

- IIC-bus compliant serial interface circuit (Multi-master type)

- ROM correction function

- 12-source 8-vectored interrupt system

- Integrated system clock generator and display clock generator

- Only one X'tal oscillator (32.768kHz) for PLL reference is used for both generators

All of the above functions are fabricated on a single chip.

The program is rewritable by using the on-board writing system after the LSI has been installed on the application board.

• No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- ♦ Anyone purchasing any products described or contained herein for an above-mentioned use shall :

- 1) Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use :

- 2) Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- ♦ Information (including circuit diagrams and circuit parameters) herein is for example only ; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

Note : This product includes the IIC bus interface circuit. If you intend to use the IIC bus interface, please notify us of this in advance of our receiving your program ROM code order.

Purchase of SANYO IIC components conveys a license under the Philips IIC Patents Rights to use these components in an IIC system, provided that the system conforms to the IIC Standard Specification as defined by Philips.

Trademarks

IIC is a trademark of Philips Corporation.

This production is produced and sold by SANYO under license of the Silicon Storage Technology Inc. This catalog provides information as of February 2001. Specifications and information herein are subject to change without notice.

#### SANYO Electric Co., Ltd. Semiconductor Company SYSTEM-LSI Div. System-Microcomputer Development Dep. 1-1-1, Sakata Oizumi-Machi, Gunma, JAPAN

SYSTEM-LSI 2001 2-26 M.Sato

### Features

(1) Built-in Flash Memory :

| 64K bytes                    |                    |

|------------------------------|--------------------|

| - Program ROM                | 48K bytes          |

| - Character ROM              | 16K bytes          |

| - Rewritable in page units   | 128 bytes / page   |

| - Page erase / program cycle | 100 cycle per page |

(2) Built-in Random Access Memory (RAM) :  $640 \times 8$  bits (including 128 bytes for ROM correction function)  $176 \times 9$  bits (for CRT display)

The LC86F3548A consists of 48K of ROM space and 640 bytes of RAM space. For this microcontroller, the usable program ROM capacity and RAM capacity are the same size for the mask ROM version.

| Mask ROM versions<br>compatible with the<br>LC86F3548A | Program ROM limit set<br>for the LC86F3548A | RAM limit set for the<br>LC86F3548A (including<br>128 bytes for the ROM<br>correction function) |

|--------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------|

| LC863548                                               | 49152 bytes                                 | 640 bytes                                                                                       |

| LC863540                                               | 40960 bytes                                 | 640 bytes                                                                                       |

| LC863532                                               | 32768 bytes                                 | 512 bytes                                                                                       |

| LC863528                                               | 28672 bytes                                 | 512 bytes                                                                                       |

| LC863524                                               | 24576 bytes                                 | 512 bytes                                                                                       |

| LC863520                                               | 20480 bytes                                 | 512 bytes                                                                                       |

| LC863516                                               | 16384 bytes                                 | 512 bytes                                                                                       |

When using on-board rewriting system is selected by the option, the rewriting program (loader program) is allocated in the last 2K-byte of the memory ,following to 46k-byte (B800h)

#### (3) OSD functions

| - Screen display           | : 36 characters                       | $\times$ 16 lines (by software)                                               |

|----------------------------|---------------------------------------|-------------------------------------------------------------------------------|

| - RAM                      | : 176 words (9                        | bits per word)                                                                |

| Display area               | : 36 words $\times$ 4                 | lines                                                                         |

| Control area               | : 8 words $\times$ 4 li               | nes                                                                           |

| - Characters               |                                       |                                                                               |

| Up to 252 kinds            | of $16 \times 32$ dot c               | haracter fonts                                                                |

|                            | (4 characters ir                      | cluding 1 test character are not programmable)                                |

| Each font can be           | e divided into tw                     | o parts and used as two fonts (Ex. $16 \times 16$ dot font $\times 2$ )       |

| - Various character attr   | ibutes                                |                                                                               |

| Character colors           | b .                                   | : 16 colors (analog mode: lv <sub>p-p</sub> output) / 8 colors (digital mode) |

| Character backg            | round colors                          | : 16 colors (analog mode: lv <sub>p-p</sub> output) / 8 colors (digital mode) |

| Fringe / shadow            | colors                                | : 16 colors (analog mode: lv <sub>p-p</sub> output) / 8 colors (digital mode) |

| Full screen color          | rs                                    | : 16 colors (analog mode: lv <sub>p-p</sub> output) / 8 colors (digital mode) |

| - Attribute can be changed | ged without spac                      | ring                                                                          |

| - Vertical display start   | line number can                       | be set for each row independently (Rows can be overlapped)                    |

|                            |                                       | e set for each row independently                                              |

| - Horizontal pitch (bit 9  | $\theta$ - 16) <sup>*1</sup> and vert | ical pitch (bit-32) can be set for each row independently                     |

|                            |                                       | each row independently                                                        |

|                            | mode / OSD mo                         | ode 1 / OSD mode 2 (Quarter size) / Simplifed graphic mode                    |

| - Ten character sizes *1   |                                       |                                                                               |

| Horiz. $\times$ Vert. =    | $(1 \times 1), (1 \times 2)$          | 2), $(2 \times 2)$ , $(2 \times 4)$ , $(0.5 \times 0.5)$                      |

|                            | $(1.5 \times 1), (1.5)$               | $5 \times 2$ ), $(3 \times 2)$ , $(3 \times 4)$ , $(0.75 \times 0.5)$         |

| - Shuttering and scrolli   | ng on each row                        |                                                                               |

| - Simplified Graphic D     | isplay                                |                                                                               |

| *1 Note : range depend     | s on display mod                      | le : refer to the manual for details.                                         |

(4) Bus Cycle Time / Instruction-Cycle Time

| Bus cycle time | Instruction cycle time | Clock divider | System clock oscillation | Oscillation Frequency | Voltage      |

|----------------|------------------------|---------------|--------------------------|-----------------------|--------------|

| 0.424µs        | 0.848µs                | 1/2           | Internal VCO             | 14.156MHz             | 4.5V to 5.5V |

| 7.5µs          | 15.0µs                 | 1/2           | Internal RC              | 800kHz                | 4.5V to 5.5V |

| 91.55µs        | 183.1µs                | 1/1           | Crystal                  | 32.768kHz             | 4.5V to 5.5V |

| 183.1µs        | 366.2µs                | 1/2           | Crystal                  | 32.768kHz             | 4.5V to 5.5V |

(5) Ports

Input / Output Ports : 4 ports (24 terminals)

Data direction programmable in nibble units : 1 port (8 terminals)

(If the N-ch open drain output is selected by option, the corresponding port data can be read in output mode.)

Data direction programmable for each bit individually : 3 ports (16 terminals)

(6) AD converter

4 channels  $\times$  6-bit AD converters

(7) Serial interfaces

- IIC-bus compliant serial interface (Multi-master type)

Consists of a single built-in circuit with two I/O channels.

The two data lines and two clock lines can be connected internally.

#### (8) PWM output

- 3 channels  $\times$  7-bit PWM

#### (9) Timer

- Timer 0 : 16-bit timer/counter

With 2-bit prescaler + 8-bit programmable prescaler

Mode 0: Two 8-bit timers with a programmable prescaler

- Mode 1: 8-bit timer with a programmable prescaler + 8-bit counter

- Mode 2: 16-bit timer with a programmable prescaler

Mode 3 : 16-bit counter

The resolution of timer is 1 tCYC.

- Timer 1 : 16-bit timer/PWM

- Mode 0 : Two 8-bit timers

Mode 1 : 8-bit timer + 8-bit PWM

- Mode 2 : 16-bit timer

- Mode 3 : Variable bit PWM (9 to 16 bits)

In mode0/1, the resolution of Timer1/PWM is 1 tCYC

In mode2/3,the resolution is selectable by program; tCYC or 1/2 tCYC

- Base timer

Generate every 500ms overflow for a clock application (using 32.768kHz crystal oscillation for the base timer clock)

Generate every 976µs, 3.9ms, 15.6ms, 62.5ms overflow (using 32.768kHz crystal oscillation for the base timer clock)

Clock for the base timer is selectable from 32.768kHz crystal oscillation, system clock or programmable prescaler output of Timer 0

- (10) Remote control receiver circuit (connected to the P73/INT3/T0IN terminal)

- Noise rejection function

- Polarity switching

#### (11) Watchdog timer

External RC circuit is required Interrupt or system reset is activated when the timer overflows

- (12) ROM correction function

- Max 128 bytes / 2 addresses

- (13) Interrupts

- 12 source 8 vectored interrupts

- 1. External Interrupt INT0

- 2. External Interrupt INT1

- 3. External Interrupt INT2, Timer/counter T0L (Lower 8 bits)

- 4. External Interrupt INT3, base timer

- 5. Timer/counter T0H (Upper 8 bits)

- 6. Timer T1H,T1L

- 7. Vertical synchronous signal interrupt ( $\overline{VS}$ ), scan line

- 8. IIC

- Interrupt priority control

Three interrupt priorities are supported (low, high and highest) and multi-level nesting is possible. Low or high priority can be assigned to the interrupts from 3 to 8 listed above. For the external interrupt INT0 and INT1, low or highest priority can be set.

(14) Sub-routine stack level

- A maximum of 128 levels (stack is built in the internal RAM)

- (15) Multiplication/division instruction

- 16 bits  $\times$  8 bits (7 instruction cycle times)

- 16 bits / 8 bits (7 instruction cycle times)

- (16) 3 oscillation circuits

- Built-in RC oscillation circuit used for the system clock

- Built-in VCO circuit used for the system clock and OSD

- X'tal oscillation circuit used for base timer, system clock and PLL reference

- (17) Standby function

- HALT mode

The HALT mode is used to reduce the power dissipation. In this operation mode, the program execution is stopped. This mode can be released by the interrupt request or the system reset.

- HOLD mode

The HOLD mode is used to stop the oscillations; RC (internal), VCO, and X'tal oscillations. This mode can be released by the following conditions.

- Pull the reset terminal ( $\overline{\text{RES}}$ ) to low level.

- Feed the selected level to either P70/INT0 or P71/INT1.

- (18) Package

- MFP36S

- DIP36S

- (19) Development tools

- Evaluation chip: LC863096

- Emulator:

EVA86000 (main) + ECB863400 (evaluation chip board) + POD36-CABLE (cable)

+ POD36-DIP (for DIP36S)

or POD36-MFP (for MFP36S)

#### Write Flash Memory

SANYO provides special services including writing data to Flash Memory and stamping.

There is a charge for these services.

Please feel free to ask our sales persons for details.

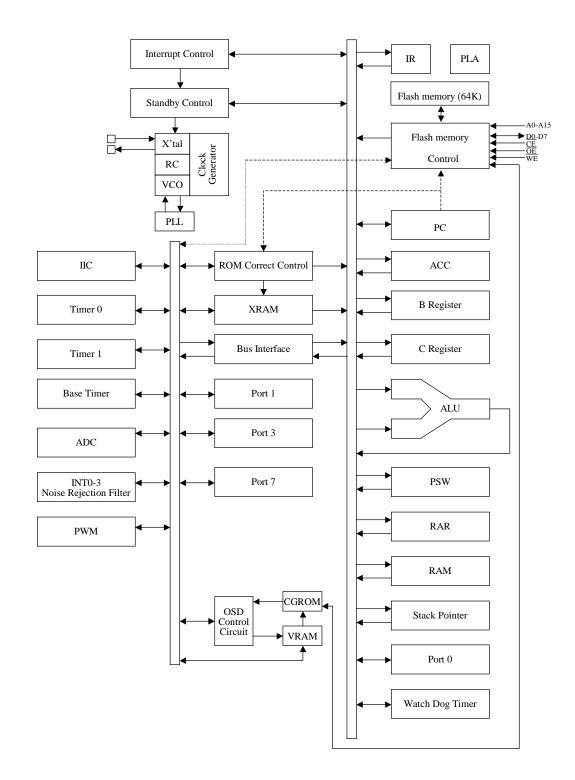

## System Block Diagram

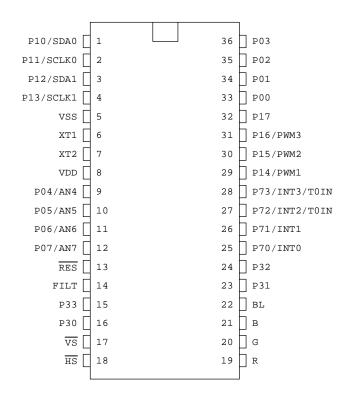

## **Pin Assignment**

## **Pin Description**

| Pin Descript |     |                                                                                      | Q i                   | <b>T</b> 1 1                                          |

|--------------|-----|--------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------|

| Terminal     | I/O | Function Description                                                                 | Option                | Flash memory mode<br>(Parallel input/<br>output mode) |

| VSS          | -   | Negative power supply                                                                |                       |                                                       |

| XT1          | Ι   | Input terminal for crystal oscillator                                                |                       |                                                       |

| XT2          | 0   | Output terminal for crystal oscillator                                               |                       |                                                       |

| VDD          | -   | Positive power supply                                                                |                       | Ī                                                     |

| RES          | Ι   | Reset terminal                                                                       |                       | Input to set up mode                                  |

| FILT         | 0   | Filter terminal for PLL                                                              |                       |                                                       |

| VS           | Ι   | Vertical synchronization signal input terminal                                       |                       | Input to set up mode                                  |

| HS           | Ι   | Horizontal synchronization signal input terminal                                     |                       |                                                       |

| R            | 0   | Red (R) output terminal of RGB image output                                          |                       | Address input A8                                      |

| G            | 0   | Green (G) output terminal of RGB image output                                        |                       | Address input A9                                      |

| В            | 0   | Blue (B) output terminal of RGB image output                                         |                       | Address input A10                                     |

| BL           | 0   | Fast blanking control signal<br>Switch TV image signal and OSD image signal          |                       | Address input A11                                     |

| Port 0       |     | •8-bit input/output port,                                                            | Pull-up resistor      | Address input                                         |

| P00 - P07    | I/O | Input/output can be specified in nibble unit                                         | provided/not provided | A0 to A7                                              |

| 100 107      | 1,0 | •Other functions                                                                     | Output Format         |                                                       |

|              |     | Interrupt input                                                                      | CMOS/Nch-OD           |                                                       |

| Port 1       |     | •8-bit input/output port                                                             | Output Format         | Data input/output                                     |

| P10 - P17    | I/O | Input/output can be specified in a bit                                               | CMOS/Nch-OD           | D0 to D7                                              |

|              |     | (programmable pull-up resister provided)                                             |                       |                                                       |

|              |     | •Other functions                                                                     |                       |                                                       |

|              |     | P10 IIC0 data I/O                                                                    |                       |                                                       |

|              |     | P11 IIC0 clock output                                                                |                       |                                                       |

|              |     | P12 IIC1 data I/O                                                                    |                       |                                                       |

|              |     | P13 IIC1 clock output                                                                |                       |                                                       |

|              |     | P14 PWM1 output<br>P15 PWM2 output                                                   |                       |                                                       |

|              |     | P15 PWM2 output<br>P16 PWM3 output                                                   |                       |                                                       |

|              |     | P17 Timer1 (PWM) output                                                              |                       |                                                       |

| D            |     |                                                                                      |                       |                                                       |

| Port 3       | I/O | •4-bit input/output port                                                             |                       | control signal WE                                     |

| P30 – P33    | 1/0 | Input/output can be specified in a bit<br>(CMOS output/input with programmable pull- |                       | control signal OE                                     |

|              |     | up resister)                                                                         |                       | control signal $\overline{CE}$                        |

|              | 1   | up residen)                                                                          | L                     | 1                                                     |

Pin Description Table

| Terminal  | I/O |                                               |                                                    | Functi                                  | on Descri  | ption      |          |        | Option        |

|-----------|-----|-----------------------------------------------|----------------------------------------------------|-----------------------------------------|------------|------------|----------|--------|---------------|

| Port 7    |     | •4-bit in                                     | put/outpu                                          | t port                                  |            |            |          |        | Address input |

| P70       | I/O | Input                                         | or output c                                        | an be spe                               | cified for | each bit   |          |        | A12 to A15    |

| P71 - P73 |     | <b>P70</b> :                                  | I/O provid                                         | led progra                              | mmable p   | ull-up res | ister    | )      |               |

|           |     | P71 t                                         | o P73: CM                                          | /IOS outpu                              | it/input w | ith progra | mmable p | ull-up |               |

|           |     | resi                                          | ister                                              |                                         |            |            |          | J      |               |

|           |     | •Other f                                      | unction                                            |                                         |            |            |          |        |               |

|           |     | Р                                             | 70 INT                                             | 0 input/H                               | OLD relea  | ise input/ |          |        |               |

|           |     |                                               | Nch                                                | -Tr. outpu                              | t for watc | hdog time  | r        |        |               |

|           |     | Р                                             | 71 INT                                             | 1 input/H                               | OLD relea  | ise input  |          |        |               |

|           |     | Р                                             | P72 INT2 input/Timer 0 event input                 |                                         |            |            |          |        |               |

|           |     | Р                                             | P73 INT3 input (noise rejection filter connected)/ |                                         |            |            |          |        |               |

|           |     | Timer 0 event input                           |                                                    |                                         |            |            |          |        |               |

|           |     | Interrupt receiver format, vector addresses   |                                                    |                                         |            |            |          |        |               |

|           |     | rising falling rising/ H level L level vector |                                                    |                                         |            |            |          | vector |               |

|           |     | falling                                       |                                                    |                                         |            |            |          |        |               |

|           |     | INT0                                          | enable enable disable enable enable 03H            |                                         |            |            |          |        |               |

|           |     | INT1                                          | enable                                             | enable enable disable enable enable 0BH |            |            |          | ]      |               |

|           |     | INT2                                          | enable                                             | enable                                  | enable     | disable    | disable  | 13H    | 1             |

|           |     | INT3                                          | enable                                             | enable                                  | enable     | disable    | disable  | 1BH    | 1             |

Note: A capacitor of at least 10µF must be inserted between VDD and VSS when using this IC.

- Output form and existence of pull-up resistor for all ports can be specified for each bit.

- Programmable pull-up resistor is always connected regardless of port option, CMOS or N-ch open drain output in port 1.

### User options

User options can be changed using Flash Memory data.

| A kind of option     | Pin, Circuits        |                                              |  |

|----------------------|----------------------|----------------------------------------------|--|

| Input/output form of | Port 0               | 1. Input : Without pull-up MOS Tr.           |  |

| input/output ports   | (Specified in a bit) | Output : N-channel open drain                |  |

|                      |                      | 2. Input : With pull-up MOS Tr.              |  |

|                      |                      | Output : CMOS                                |  |

|                      | Port 1               | 1. Input : With programmable pull-up MOS T   |  |

|                      | (Specified in a bit) | Output : N-channel open drain                |  |

|                      |                      | 2. Input : With programmable pull-up MOS Tr. |  |

|                      |                      | Output : CMOS                                |  |

### Notice for use

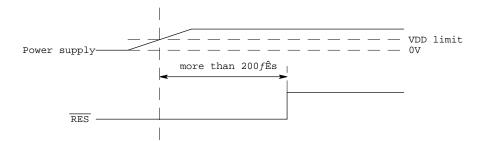

- Input level of terminal  $\overline{\text{RES}}$  at power on

Terminal  $\overline{\text{RES}}$  must be held low for at least 200µs after the supply voltage exceeds the power supply lower limit.

-difference between the Mask version and Flash version(LC86F3548A)

| 1. the operation after release of reset | : the mask version operates the program from the address 0 in the<br>program counter as soon as detecting the H level on the reset port.<br>the flash version operates the program from the address 0 in the<br>program counter after setting the option. |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. Current dissipation                  | <ul> <li>The current dissipation of the flash version is bigger than that of the mask version.</li> <li>please refer to the latest semiconductor news.</li> </ul>                                                                                         |

- Conditions during reset and after release of reset

Port options are set using Flash Memory data.

Port options are set internally within approximately 3ms after logic HIGH is applied to the RESET terminal. The configuration of the port outputs change over the duration of this period. Then the Program Counter is set to 0 and program execution begins.

During reset, and in the few hundred milliseconds after reset is released, the port options on certain of the ports will not yet have been set. The conditions of the various ports during reset or on release of reset have been collected in the following table. Please refer to it when analyzing circuits where these conditions apply.

| Pins | Options                                                                                                                                                      | Condition during and on release of reset                                                                                                                                                                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PO   | Input : Without pull up MOS<br>transistor<br>Output : N-channel open drain                                                                                   | Output -off<br>Input mode : High impedance                                                                                                                                                                                                                         |

|      | Input : With pull up MOS<br>transistor                                                                                                                       | Output-off<br>Flash version: During reset and in the first few                                                                                                                                                                                                     |

|      | Output : CMOS                                                                                                                                                | hundred µs after reset is released, the pull-up<br>MOS transistor is OFF. Thereafter, set to input<br>mode with pull-up MOS Tr. ON<br>Mask version: During reset the pull-up<br>MOS transistor is OFF.<br>After soon, set to input mode with pull-up<br>MOS Tr. ON |

| P1   | Input : With programmable pull up MOS<br>transistor<br>Output : N-channel open drain<br>Input : With programmable pull up MOS<br>transistor<br>Output : CMOS | Output-off<br>Input mode : High impedance                                                                                                                                                                                                                          |

| Р3   | No options<br>Input : With programmable pull up MOS<br>transistor<br>Output : CMOS                                                                           | Output -off<br>Input mode : High impedance                                                                                                                                                                                                                         |

| Р7   | No options<br>Input : With programmable pull up MOS<br>transistor<br>Output : With pull up MOS (P70)<br>CMOS (P71 - P73)                                     | Output-off<br>Input mode : High impedance                                                                                                                                                                                                                          |

### On-board writing system

The LC86F3548A has the On-board writing system. The program is renewable by using SANYO Flash On-board

System after the LSI has been installed on the application board.

This system is composed of 4 types divided by the combination of mode setting pin and communication pin.

Each type system has to connect the 6 pins (VDD,VSS,RES, communication pins) with the interface board of SANYO Flash On-board system.

It is necessary that the pins to be used for the rewriting system should be able to be separated from the application board properly.

The system type is selected by the option setting program (Su86K.exe).

| types | mode setting pin                         | communication pins                 |

|-------|------------------------------------------|------------------------------------|

| type1 | RES pin (high voltage(12V) applied)      | P30(DATA1),P31(DATA0),P32(CLK)     |

| type2 | RES pin (high voltage(12V) applied)      | P30(DATA1),P11(DATA0),P10(CLK)     |

| type3 | P30 pin (High level voltage (5V)applied) | P30(ENA/DATA1),P31(DATA0),P32(CLK) |

| type4 | P30 pin (High level voltage (5V)applied) | P30(ENA/DATA1),P11(DATA0),P10(CLK) |

• Type 3 or 4 is selected : P30 is exclusive for the on-board system. This pin must always be pulled-down, so this pin can't be used for other applications.

• The loader program must be written into the ROM to use On-board writing system.

The loader program should be written into the ROM before the LSI has been installed on the board by the the general purpose ROM programs.

When the option setting selects the this system to use, the loader program automatically links on the user program linking.

Please ask to our sales persons before using On-board writing system.

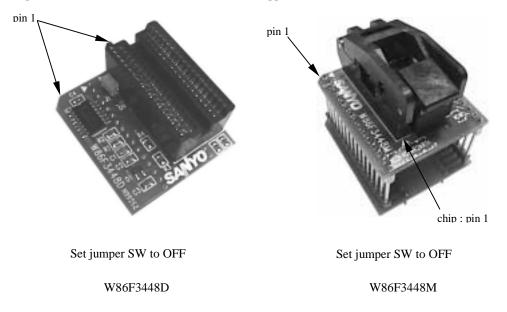

### **Use of PROM Conversion board**

When reading or writing data to the LC86F3548A using our exclusive conversion board (W86F3448D, W86F3448M) general purpose PROM programs can be used.

(1) Name of conversion boards

- W86F3448D • DIP36S purpose

- W86F3448M • MFP36S purpose

(2) Available PROM programmers

The LC86F3548A does not support a silicon signature feature. Do not use the feature (automatic device type selection) when programming this device. To avoid erasing the program, confirm the setting of the protection for written program is active before using .

Single word write

| Manufacture        | Name of device       | version | applicable device (code)      | Data protection     |

|--------------------|----------------------|---------|-------------------------------|---------------------|

|                    |                      |         |                               | setting after write |

|                    |                      |         |                               | operation           |

| Minato Electronics | MODEL 1890A + OU-910 | V4.1    | SST Co., Ltd. 29EE512 (D617)  | Protected           |

| Ando               | AF-9708              | 01.00   | SST Co., Ltd. 29EE512 (47100) | Protected           |

| Data I. O.         | ChipLab              | V5.3    | SST Co., Ltd. 29EE512         | Selectable          |

### Write multiple words

| Manufacture        | Name of device         | version | applicable device (code)     | Data protection<br>setting after write<br>operation |

|--------------------|------------------------|---------|------------------------------|-----------------------------------------------------|

| Minato Electronics | MODEL 1892 + TYPE9102A | V4.1    | SST Co., Ltd. 29EE512 (D617) | Protected                                           |

(3) Notes

When using the conversion board, all of the jumper SW must be set to the OFF position. If set to the ON position, read/write operations will not perform correctly.

(4) Location of pin 1

Pin 1 of the conversion board should be located as indicated below.

W86F3448D : when viewing from the edge closest to jumper SW, pin 1 is located on the upper left of both the chip and conversion board.

W86F3448M : when viewing from the edge closest to jumper SW, pin 1 of the chip is located on the lower left while pin 1 of the conversion board is located on the upper left.

| Para                            | meter           | Symbol           | Pins                                                                        | Conditions                     |        | Limits |      |         |      |

|---------------------------------|-----------------|------------------|-----------------------------------------------------------------------------|--------------------------------|--------|--------|------|---------|------|

|                                 |                 | 5                |                                                                             |                                | VDD[V] | min.   | typ. | max.    | unit |

| Supply vo                       | oltage          | VDDMAX           | VDD                                                                         |                                |        | -0.3   |      | +6.0    | V    |

| Input volt                      | age             | VI(1)            | $\bullet \overline{\text{RES}}, \overline{\text{HS}}, \overline{\text{VS}}$ |                                |        | -0.3   |      | VDD+0.3 |      |

| Output vo                       | oltage          | VO(1)            | R, G, B, BL,<br>FILT                                                        |                                |        | -0.3   |      | VDD+0.3 |      |

| Input/out<br>voltage            | put             | VIO              | •Ports 0, 1, 3, 7                                                           |                                |        | -0.3   |      | VDD+0.3 |      |

| High<br>level                   | Peak<br>output  | IOPH(1)          | •Ports 0, 1, 3, 7                                                           | •CMOS output<br>•For each pin. |        | -4     |      |         | mA   |

| output<br>current               | current         | IOPH(2)          | R, G, B, BL                                                                 | •CMOS output<br>•For each pin. |        | -5     |      |         |      |

|                                 | Total<br>output | $\Sigma$ IOAH(1) | •Ports 0, 1                                                                 | The total of all pins.         |        | -20    |      |         |      |

|                                 | current         | $\Sigma$ IOAH(2) | Ports 3,7                                                                   | The total of all pins.         |        | -10    |      |         |      |

|                                 |                 | $\Sigma$ IOAH(3) | R, G, B, BL                                                                 | The total of all pins.         |        | -12    |      |         |      |

| Low                             | Peak            | IOPL(1)          | Ports 0, 1, 3,7                                                             | For each pin.                  |        |        |      | 20      |      |

| level                           | output          | IOPL(2)          | Port 7                                                                      | For each pin.                  |        |        |      | 15      |      |

| output                          | current         | IOPL(3)          | R, G, B, BL                                                                 | For each pin.                  |        |        |      | 5       |      |

| current                         | Total<br>output | $\Sigma$ IOAL(1) | Ports 0, 1                                                                  | The total of all pins.         |        |        |      | 40      |      |

|                                 | current         | $\Sigma$ IOAL(2) | Ports 3, 7                                                                  | The total of all pins.         |        |        |      | 30      |      |

|                                 |                 | $\Sigma$ IOAL(3) | R, G, B, BL                                                                 | The total of all pins.         |        |        |      | 15      |      |

| Maximun                         | n power         | Pdmax            | MFP36S                                                                      | Ta=-10 to +70°C                |        |        |      | 380     | mW   |

| dissipatio                      | n               |                  | DIP36S                                                                      |                                |        |        | 560  |         |      |

| Operating<br>temperatu<br>range |                 | Topg             |                                                                             |                                |        | -10    |      | +70     | °C   |

| Storage<br>temperatu<br>range   | ıre             | Tstg             |                                                                             |                                |        | -55    |      | +125    |      |

## 1. Absolute maximum ratings / VSS=0V and Ta=25°C

| Parameter                         | Symbol  | Pins                                                                                               | Conditions                                                                       |           | Limits  |       |         |         |

|-----------------------------------|---------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------|---------|-------|---------|---------|

|                                   |         |                                                                                                    |                                                                                  | VDD[V]    | min.    | typ.  | max.    | unit    |

| Operating<br>supply voltage       | VDD(1)  | VDD                                                                                                | 0.844µs ≤ tCYC<br>≤ 0.852µs                                                      |           | 4.5     |       | 5.5     | V       |

| range                             | VDD(2)  |                                                                                                    | $4\mu s \le tCYC \le 400\mu s$                                                   |           | 4.5     |       | 5.5     |         |

| Hold voltage                      | VHD     | VDD                                                                                                | RAMs and the<br>registers data are<br>kept in HOLD<br>mode.                      |           | 2.0     |       | 5.5     |         |

| High level input voltage          | VIH(1)  | Port 0                                                                                             | Output disable                                                                   | 4.5 - 5.5 | 0.6VDD  |       | VDD     |         |

|                                   | VIH(2)  | •Ports 1,3 (Schumitt)<br>•Port 7 (Schumitt)<br>port input/interrupt<br>• HS, VS, RES<br>(Schumitt) | Output disable                                                                   | 4.5 - 5.5 | 0.75VDD |       | VDD     |         |

|                                   | VIH(3)  | Port 70<br>Watchdog timer input                                                                    | Output disable                                                                   | 4.5 - 5.5 | VDD-0.5 |       | VDD     |         |

| Low level                         | VIL(1)  | Port 0 (Schumitt)                                                                                  | Output disable                                                                   | 4.5 - 5.5 | VSS     |       | 0.2VDD  |         |

| input voltage                     | VIL(2)  | Ports 1,3 (Schumitt)     Port 7 (Schumitt)     port input/interrupt     HS, VS, RES     (Schumitt) | Output disable                                                                   | 4.5 - 5.5 | VSS     |       | 0.25VDD |         |

|                                   | VIL(3)  | Port 70<br>Watchdog timer input                                                                    | Output disable                                                                   | 4.5 - 5.5 | VSS     |       | 0.6VDD  |         |

| Operation cycle time              | tCYC(1) |                                                                                                    | •All functions operating                                                         | 4.5 - 5.5 | 0.844   | 0.848 | 0.852   | μs      |

|                                   | tCYC(2) |                                                                                                    | <ul> <li>AD converter<br/>operating</li> <li>OSD is not<br/>operating</li> </ul> | 4.5 - 5.5 | 0.844   |       | 30      |         |

|                                   | tCYC(3) |                                                                                                    | •OSD and AD<br>converter are<br>not operating                                    | 4.5 - 5.5 | 0.844   |       | 400     |         |

| Oscillation<br>frequency<br>range | FmRC    |                                                                                                    | Internal RC oscillation                                                          | 4.5 - 5.5 | 0.4     | 0.8   | 3.0     | MH<br>z |

| Parameter                                                                | Symbol  | Pins                                                                           | Conditions                                                                                                          | -         | Limits  |        |      |      |

|--------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------|---------|--------|------|------|

|                                                                          |         |                                                                                |                                                                                                                     | VDD[V]    | min.    | typ.   | max. | unit |

| High level<br>input current                                              | IIH(1)  | Ports 0, 1, 3, 7                                                               | •Output disable<br>•Pull-up MOS Tr.<br>OFF<br>•VIN=VDD<br>(including the off-<br>leak current of the                | 4.5 - 5.5 |         |        | 1    | μA   |

|                                                                          | IIH(2)  |                                                                                | output Tr.)<br>•VIN=VDD                                                                                             | 4.5 - 5.5 |         |        | 1    | •    |

|                                                                          | IIII(2) | • $\overline{\text{RES}}$<br>• $\overline{\text{HS}}$ , $\overline{\text{VS}}$ | • v IIv= v DD                                                                                                       | 4.5 - 5.5 |         |        | 1    |      |

| Low level<br>input current                                               | IIL(1)  | Ports 0, 1, 3, 7                                                               | •Output disable<br>•Pull-up MOS<br>Tr. OFF<br>•VIN=VSS<br>(including the off-<br>leak current of the<br>output Tr.) | 4.5 - 5.5 | -1      |        |      |      |

|                                                                          | IIL(2)  | • $\overline{\text{RES}}$<br>• $\overline{\text{HS}}$ , $\overline{\text{VS}}$ | VIN=VSS                                                                                                             | 4.5 - 5.5 | -1      |        |      |      |

| High level<br>output voltage                                             | VOH(1)  | •CMOS output of ports 0, 1, 3, 71 - 73                                         | IOH=-1.0mA                                                                                                          | 4.5 - 5.5 | VDD-1   |        |      | V    |

|                                                                          | VOH(2)  | R, G, B, BL                                                                    | IOH=-0.1mA<br>RGB: digital mode                                                                                     | 4.5 - 5.5 | VDD-0.5 |        |      | -    |

| Low level output voltage                                                 | VOL(1)  | Ports 0, 1, 3,<br>71 - 73                                                      | IOL=10mA                                                                                                            | 4.5 - 5.5 |         |        | 1.5  |      |

|                                                                          | VOL(2)  | Ports 0, 3,<br>71 - 73                                                         | IOL=1.6mA                                                                                                           | 4.5 - 5.5 |         |        | 0.4  |      |

|                                                                          | VOL(3)  | •R, G, B, BL<br>•Port 1                                                        | IOL=3.0mA<br>RGB: digital mode                                                                                      | 4.5 - 5.5 |         |        | 0.4  |      |

|                                                                          | VOL(4)  | Port 70                                                                        | IOL=1mA                                                                                                             | 4.5 - 5.5 |         |        | 0.4  |      |

| Pull-up MOS<br>Tr. resistance                                            | Rpu     | •Ports 0, 1, 3, 7                                                              | VOH=0.9VDD                                                                                                          | 4.5 - 5.5 | 13      | 38     | 80   | kΩ   |

| Bus terminal<br>short circuit<br>resistance<br>(SCL0-SCL1,<br>SDA0-SDA1) | RBS     | •P10-12<br>•P11-13                                                             |                                                                                                                     | 4.5 - 5.5 |         |        | 130  | Ω    |

| Hysteresis<br>voltage                                                    | VHIS    | •Ports 1, 3, 7<br>• RES<br>• HS , VS                                           | Output disable                                                                                                      | 4.5 - 5.5 |         | 0.1VDD |      | V    |

| Pin<br>capacitance                                                       | СР      | All pins                                                                       | •f=1MHz<br>•Every other<br>terminals are<br>connected to VSS.<br>•Ta=25°C                                           | 4.5 - 5.5 |         | 10     |      | pF   |

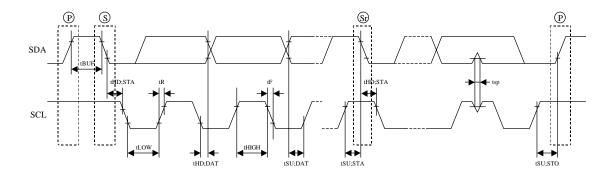

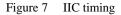

## 4. IIC input/output conditions / Ta=-10°C to +70°C, VSS=0V

| Parameter                             | Symbol  | Star | ndard | High s  | speed | unit |

|---------------------------------------|---------|------|-------|---------|-------|------|

|                                       |         | min. | max.  | min.    | max.  |      |

| SCL Frequency                         | fSCL    | 0    | 100   | 0       | 400   | kHz  |

| BUS free time between stop - start    | tBUF    | 4.7  | -     | 1.3     | -     | μs   |

| HOLD time of start, restart condition | tHD;STA | 4.0  | -     | 0.6     | -     | μs   |

| L time of SCL                         | tLOW    | 4.7  | -     | 1.3     | -     | μs   |

| H time of SCL                         | tHIGH   | 4.0  | -     | 0.6     | -     | μs   |

| Set-up time of restart condition      | tSU;STA | 4.7  | -     | 0.6     | -     | μs   |

| HOLD time of SDA                      | tHD;DAT | 0    | -     | 0       | 0.9   | μs   |

| Set-up time of SDA                    | tSU;DAT | 250  | -     | 100     | -     | ns   |

| Rising time of SDA, SCL               | tR      | -    | 1000  | 20+0.1C | 300   | ns   |

|                                       |         |      |       | b       |       |      |

| Falling time of SDA, SCL              | tF      | -    | 300   | 20+0.1C | 300   | ns   |

|                                       |         |      |       | b       |       |      |

| Set-up time of stop condition         | tSU;STO | 4.0  | -     | 0.6     | -     | μs   |

Refer to figure 7

(Note) Cb : Total capacitance of all BUS (unit : pF)

## 5. Pulse input conditions / Ta=-10°C to +70°C, VSS=0V

| Parameter           | Symbol             | Pins                                                                | Conditions                                                                                                                                                                |           | Limits |      |      |      |

|---------------------|--------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|------|------|------|

|                     |                    |                                                                     |                                                                                                                                                                           | VDD[V]    | min.   | typ. | max. | unit |

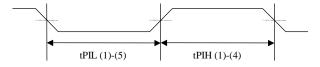

| High/low<br>level   | tPIH(1)<br>tPIL(1) | •INT0, INT1<br>•INT2/T0IN                                           | •Interrupt acceptable<br>•Timer0-countable                                                                                                                                | 4.5 - 5.5 | 1      |      |      | tCYC |

| pulse width         | tPIH(2)<br>tPIL(2) | INT3/T0IN<br>(1 tCYC is<br>selected for noise<br>rejection clock.)  | •Interrupt acceptable<br>•Timer0-countable                                                                                                                                | 4.5 - 5.5 | 2      |      |      |      |

|                     | tPIH(3)<br>tPIL(3) | INT3/T0IN<br>(16 tCYC is<br>selected for noise<br>rejection clock.) | •Interrupt acceptable<br>•Timer0-countable                                                                                                                                | 4.5 - 5.5 | 32     |      |      |      |

|                     | tPIH(4)<br>tPIL(4) | INT3/T0IN<br>(64 tCYC is<br>selected for noise<br>rejection clock.) | •Interrupt acceptable<br>•Timer0-countable                                                                                                                                | 4.5 - 5.5 | 128    |      |      |      |

|                     | tPIL(5)            | RES                                                                 | Reset acceptable                                                                                                                                                          | 4.5 - 5.5 | 200    |      |      | μs   |

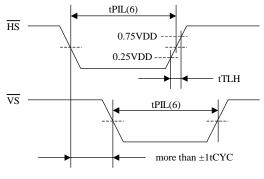

|                     | tPIH(6)<br>tPIL(6) | HS, VS                                                              | <ul> <li>Display position<br/>controllable (Note)</li> <li>The active edge of<br/>HS and VS must<br/>be apart at least<br/>1 tCYC.</li> <li>Refer to figure 4.</li> </ul> | 4.5 - 5.5 | 8      |      |      |      |

| Rising/falling time | tTHL<br>tTLH       | HS                                                                  | Refer to figure 4.                                                                                                                                                        | 4.5 - 5.5 |        |      | 500  | ns   |

| Parameter                     | Symbol | Pins                                | Conditions                                        |           | Limits | Limits |      |      |

|-------------------------------|--------|-------------------------------------|---------------------------------------------------|-----------|--------|--------|------|------|

|                               |        |                                     |                                                   | VDD[V]    | min.   | typ.   | max. | unit |

| Resolution                    | Ν      |                                     |                                                   | 4.5 - 5.5 |        | 6      |      | bit  |

| Absolute precision            | ET     |                                     | (Note)                                            |           |        |        | ±1   | LSB  |

| Conversion<br>time            | tCAD   | Vref selection to conversion finish | 1 bit conversion time<br>= $2 \times \text{Tcyc}$ |           |        | 1.69   |      | μs   |

| Analog input<br>voltage range | VAIN   | AN4 - AN7                           |                                                   | ]         | VSS    |        | VDD  | V    |

| Analog port                   | IAINH  |                                     | VAIN=VDD                                          |           |        |        | 1    | μA   |

| input current                 | IAINL  | Ī                                   | VAIN=VSS                                          | ]         | -1     |        |      |      |

## 6. AD converter characteristics / Ta=-10°C to + 70°C, VSS=0V

(Note) Absolute precision does not include quaritizing error (1/2LSB).

## 7. Analog mode RGB characteristics / Ta=-10°C to +70°C, VSS=0V

| Parameter     | Symbol | Pins               | Conditions       |        | Limits |      |      |      |

|---------------|--------|--------------------|------------------|--------|--------|------|------|------|

|               |        |                    |                  | VDD[V] | min.   | typ. | max. | unit |

| Analog output |        | R.G.B              | Low level output | 5.0    | 0.45   | 0.5  | 0.55 | V    |

| voltage       |        | Analog output mode | Intensity output |        | 0.90   | 1.0  | 1.10 |      |

|               |        |                    | Hi lebel output  |        | 1.35   | 1.5  | 1.65 |      |

| Time setting  |        | R.G.B              | 70%              |        |        |      | 50   | ns   |

|               |        |                    | 10pf load        |        |        |      |      |      |

# 8. Sample current dissipation characteristics / Ta=-10°C to +70°C, VSS=0V

The sample current dissipation characteristics is the measurement result of Sanyo provided evaluation board when the recommended circuit parameters shown in the sample oscillation circuit characteristics are used externally. The currents through the output transistors and the pull-up MOS transistors are ignored.

| Parameter                                        | Symbol     | Pins | Conditions                                                                                                                                                                                              |           | Limits |      |      |      |

|--------------------------------------------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|------|------|------|

|                                                  | 2          |      |                                                                                                                                                                                                         | VDD[V]    | min.   | typ. | max. | unit |

| Current dissipation<br>during basic<br>operation | IDDOP(1)   | VDD  | <ul> <li>FmX'tal=32.768kHz<br/>X'tal oscillation</li> <li>System clock :<br/>VCO</li> <li>VCO for OSD<br/>operating</li> <li>OSD : digital mode</li> <li>Internal RC<br/>oscillation stops</li> </ul>   | 4.5 - 5.5 |        | 27   | 44   | mA   |

|                                                  | IDDOP(2)   | VDD  | <ul> <li>FmX'tal=32.768kHz<br/>X'tal oscillation</li> <li>System clock :<br/>VCO</li> <li>VCO for OSD<br/>operating</li> <li>OSD : analog mode</li> <li>Internal RC<br/>oscillation stops</li> </ul>    | 4.5 - 5.5 |        | 35   | 55   | μΑ   |

|                                                  | IDDOP(3)   | VDD  | <ul> <li>FmX'tal=32.768kHz<br/>X'tal oscillation</li> <li>System clock :<br/>X'tal</li> <li>VCO for system<br/>VCO for OSD,<br/>internal RC<br/>oscillation stop</li> <li>AD converters stop</li> </ul> | 4.5 - 5.5 |        | 100  | 300  | μΑ   |

| Current dissipation<br>in HALT mode              | IDDHALT(1) | VDD  | <ul> <li>HALT mode</li> <li>FmX'tal=32.768kHz<br/>X'tal oscillation</li> <li>System clock :<br/>VCO</li> <li>VCO for OSD stops</li> <li>Internal RC<br/>oscillation stops</li> </ul>                    | 4.5 - 5.5 |        | 6    | 10   | mA   |

|                                                  | IDDHALT(2) | VDD  | <ul> <li>HALT mode</li> <li>FmX'tal=32.768kHz<br/>X'tal oscillation</li> <li>VCO for system<br/>stops</li> <li>VCO for OSD stops</li> <li>System clock :<br/>Internal RC</li> </ul>                     | 4.5 - 5.5 |        | 430  | 1000 | μΑ   |

|                                                  | IDDHALT(3) | VDD  | <ul> <li>HALT mode</li> <li>FmX'tal=32.768kHz<br/>X'tal oscillation</li> <li>VCO for system<br/>stops</li> <li>VCO for OSD stops</li> <li>System clock : X'tal</li> </ul>                               | 4.5 - 5.5 |        | 60   | 200  |      |

| Current dissipation<br>in HOLD mode              | IDDHOLD    | VDD  | •HOLD mode<br>•All oscillation stops.                                                                                                                                                                   | 4.5 - 5.5 |        | 0.05 | 20   | μA   |

(Note 3) The currents of the output transistors and the pull-up MOS transistors are ignored.

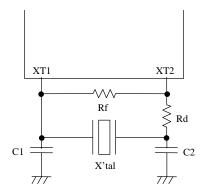

Recommended Oscillation Circuit and Sample Characteristics

The sample oscillation circuit characteristics in the table below is based on the following conditions:

- Recommended circuit parameters are verified by an oscillator manufacturer using a Sanyo provided oscillation evaluation board.

- Sample characteristics are the result of the evaluation with the recommended circuit parameters connected externally.

| Frequency | Manufacturer | Oscillator | Recommended circuit si parameters |      | Operating<br>supply voltage<br>range | Oscillation stabilizing time |            | Notes |       |  |

|-----------|--------------|------------|-----------------------------------|------|--------------------------------------|------------------------------|------------|-------|-------|--|

|           |              |            | C1                                | C2   | C2 Rf Rd                             |                              | Tange      | typ.  | max   |  |

| 32.768kHz | Seiko Epson  | C-002RX    | 18pF                              | 18pF | open                                 | 390k•                        | 4.5 - 5.5V | 1.00s | 1.50s |  |

Recommended oscillation circuit and sample characteristics (Ta = -10 to  $+70^{\circ}$ C)

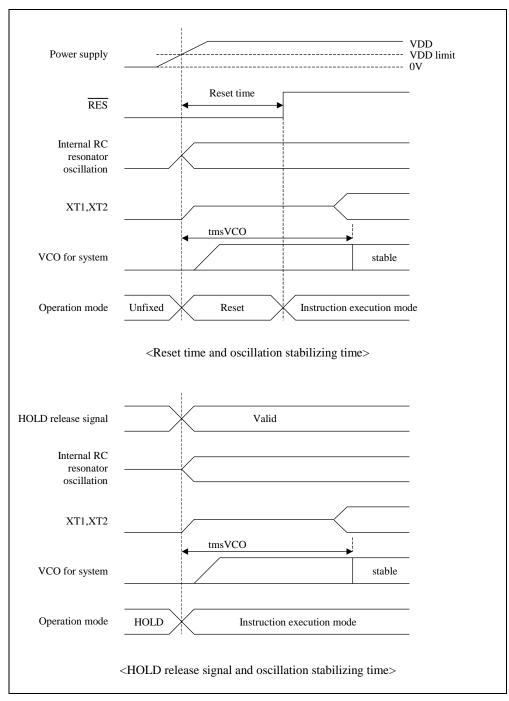

Notes The oscillation stabilizing time period is the time until the VCO oscillation for the internal system becomes stable after the following conditions. (Refer to Figure 2.)

- 1. The VDD becomes higher than the minimum operating voltage after the power is supplied.

- 2. The HOLD mode is released.

The sample oscillation circuit characteristics may differ applications. For further assistance, please contact with oscillator manufacturer with the following notes in your mind.

- Since the oscillation frequency precision is affected by wiring capacity of the application board, etc., adjust the oscillation frequency on the production board.

- The above oscillation frequency and the operating supply voltage range are based on the operating temperature of  $-10^{\circ}$ C to  $+70^{\circ}$ C. For the use with the temperature outside of the range herein, or in the applications requiring high reliability such as car products, please consult with oscillator manufacturer.

- When using the oscillator which is not shown in the sample oscillation circuit characteristics, please consult with Sanyo sales personnel.

Since the oscillation circuit characteristics are affected by the noise or wiring capacity because the circuit is designed with low gain in order to reduce the power dissipation, refer to the following notices.

- The distance between the clock I/O terminal (XT1 terminal XT2 terminal) and external parts should be as short as possible.

- The capacitors' VSS should be allocated close to the microcontroller's GND terminal and be away from other GND.

- The signal lines with rapid state changes or with large current should be allocated away from the oscillation circuit.

Figure 1 Recommended oscillation circuit.

Figure 2 Oscillation stabilizing time

Figure 3 Pulse input timing condition – 1

Figure 4 Pulse input timing condition - 2

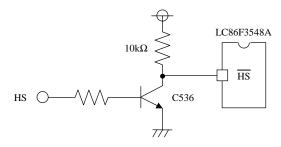

Figure 5 Recommended Interface circuit

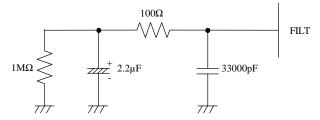

(Note) Place FILT parts on board as close to the microcontroller as possible.

S : start condition P : stop condition Sr : restart condition

Standard mode : not exist High speed mode : less than 50ns

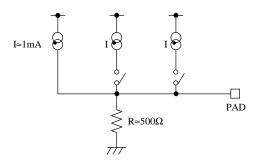

Figure 8 R.G.B. analog output equivalent circuit