#### **General Description**

The LZC811 is a single-power stage, isolated and primary side offline LED lighting regulator which achieves high power factor. The proprietary real-current control method can control the LED current accurately from the primary side information. It can significantly simplify the LED lighting system design by eliminating the secondary side feedback components and the opto-coupler. The LZC811 integrates active power factor correction and works in Quasi Resonance mode (QRM) in order to reduce the MOSFET switching losses. With a building in 700V start-up MOSFET, IC can eliminate the power loss caused by start-up resistors to provide a high efficiency solution for lighting applications. The external programmable line voltage compensation provides a more precise output current throughout the universal AC input voltage range. The leading edge blanking circuit on the CS/FB input removes the signal glitch and results in reduced external components and system cost. The multi-protection features of LZC811 greatly enhance the system reliability and safety. The LZC811 features VDD and output over voltage protection; output short circuit protection, cycle-by-cycle current limit and secondary peak current protection on CS pin, VDD UVLO and auto-restart and over-temperature protection. The driver output voltage is clamped at 18V to protect the external power MOSFET.

Fly-back topology

- Real-Current control to meet accurate

output current

- Very less components

- Programmable input AC voltage compensation

- Leading Edge Blanking on CS/FB pin

- Protection Features

- Building in hysteresis OTP

- VDD over voltage protection

- Cycle by cycle current limiting on CS pin

- Secondary peak current protection on CS pin

- > Output short to GND protection

- Output programmable over voltage protection

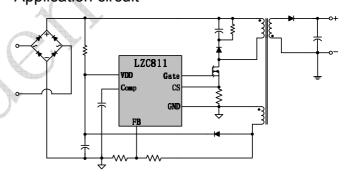

- > FB and CS pins default protection Application circuit

#### Features

- Single stage PFC

- Primary side regulation without Secondary Feedback

- Quasi Resonance (QR) mode with

Confidential Page 1

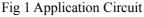

Pin Assignment

## **Absolute Maximum Rating**

| Symbol                                                               | Parameter                         | Rating         |  |

|----------------------------------------------------------------------|-----------------------------------|----------------|--|

| V <sub>DD</sub>                                                      | Maximum supply voltage on VDD pin | 28.0V          |  |

| V <sub>FB</sub>                                                      | -0.3V to 6.0V                     |                |  |

| V <sub>CS</sub>                                                      | Input Voltage to CS Pin           | -0.3V to 6.0V  |  |

| V <sub>CMP</sub> Input Voltage to CMP Pin                            |                                   | -0.3V to 6.0V  |  |

| ESD Capability                                                       | HBM Model                         | >2000V         |  |

|                                                                      | Machine Model                     | >200V          |  |

| T <sub>Max</sub> Maximum Operating Junction Temperature <sup>3</sup> |                                   | 125°C          |  |

| T <sub>STG</sub>                                                     | Storage Temperature Range         | -55°C to 150°C |  |

Block Diagram

### Pin Functions

| Pin Fur | ictions |            |                                                                                                                                                              |  |

|---------|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name    | I/O     | Pin<br>No. | Description                                                                                                                                                  |  |

| CMP     | I       | 1          | Loop compensation for constant current regulation. Output of the OTA.<br>The RC network is placed between it and GND.                                        |  |

| FB      | I/O     | 2          | Detect output diode zero current to regulate output current.<br>Connected to a resistor divider for sensing the reflected voltage from<br>auxiliary winding. |  |

| CS      | I       | 3          | Current sense pin, a resistor connects to sense the MOSFET current.                                                                                          |  |

| GND     | Power   | 4          | Power Ground.                                                                                                                                                |  |

| DRV     | 0       | 5          | Totem-pole output to drive the external power MOSFET, Maximum Voltage is internally clamped to 18V.                                                          |  |

| VDD     | Power   | 6          | Power Supply.                                                                                                                                                |  |

| NC      | /       | 7          | No connect.                                                                                                                                                  |  |

| NC      |         | 8          | No connect.                                                                                                                                                  |  |

|         |         | 100        |                                                                                                                                                              |  |

## **Electrical Characteristics**

(T\_A=25 $^\circ\!\!\!\mathrm{C}$  and VDD=15V if not otherwise noted)

| Querra ha a l                   | Parameter                      | Test Conditions     | Limits     |      |      |       |

|---------------------------------|--------------------------------|---------------------|------------|------|------|-------|

| Symbol                          |                                |                     | Min.       | Тур. | Max. | Unit  |

| VDD pin                         |                                |                     |            |      |      |       |

| I <sub>OP</sub>                 | Operating Current              | Gate open           |            | 1    |      | mA    |

| VDD <sub>ON</sub>               | Turn-on Threshold Voltage      |                     |            | 16   |      | V     |

| VDD <sub>OFF</sub>              | Turn-off Threshold Voltage     |                     |            | 9    |      | V     |

| VDD <sub>RST</sub>              | Logic Reset VDD Threshold      |                     |            | 6    |      | V     |

| VDDRSI                          | Voltage                        |                     |            | 0    |      | v     |

| VDD <sub>OVP</sub>              | VDD Over Voltage Protection    |                     |            | 25   |      | V     |

| CMP pin                         |                                |                     |            |      |      | V     |

| V <sub>REF</sub>                | Reference voltage for OTA      |                     | $\bullet$  | 0.2  | 2    | V     |

| ¥ REF                           | input                          |                     | A          | 0.2  |      | V     |

| I <sub>CMP_SINK</sub>           | CMP maximal sink current       |                     | 1          | 50   |      | uA    |

| I <sub>CMP_SOURCE</sub>         | CMP maximal source current     | X                   |            | 10   |      | uA    |

| $V_{CMP\_MAX}$                  | CMP max. voltage               |                     | $\searrow$ | 4.0  |      | V     |

| FB Pin                          |                                |                     |            |      |      |       |

| $V_{FB\_SINK}$                  | FB voltage when sink current   | 2mA sink current    |            | 5.0  |      | V     |

| V                               | FB voltage when source         | 4mA source          | -0.1       | GND  | +0.1 | V     |

| $V_{FB_SOURCE}$                 | current                        | current             |            | GND  | +0.1 |       |

| $V_{FB_ZVD}$                    | FB zero voltage detect         |                     |            | 0.2  |      | V     |

| $V_{FB_OVP}$                    | FB voltage when Output OVP     |                     |            | 3.6  |      | V     |

| $V_{FB\_SCP}$                   | FB voltage when trigger SCP    | 2                   |            | 1.0  |      | V     |

| CS Pin                          |                                |                     |            |      |      |       |

| V <sub>CS1</sub>                | Cycle by Cycle current limited | FB=0V               |            | 1    |      | V     |

| V CS1                           | on CS                          | 10-00               |            | 1    |      | v     |

| $\Delta V_{CS} / \Delta I_{FB}$ | Inner CS Voltage vary with FB  |                     |            | TBD  |      | mV/mA |

|                                 | source current                 |                     |            |      |      |       |

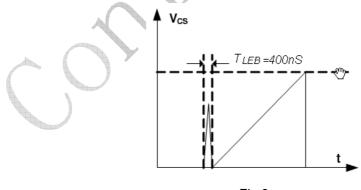

| T <sub>BLANK</sub>              | Leading-Edge Blanking Time     |                     | 300        | 400  | 500  | nS    |

| Oscillator                      |                                |                     |            | •    |      |       |

| F <sub>OSC_MAX</sub>            | Maximal Frequency              |                     |            | 130  |      | kHz   |

| F <sub>OSC_MIN</sub>            | Minimal Frequency              |                     |            | 30   |      | kHz   |

| GATE Drive C                    | Output (GATE Pin)              |                     |            |      |      |       |

| T <sub>R</sub>                  | Rise Time                      | C <sub>L</sub> =1nF |            | 200  |      | Ns    |

| T <sub>F</sub>                  | Fall Time                      | C <sub>L</sub> =1nF |            | 100  |      | Ns    |

| Over Tempera                    | ature Protection               |                     |            |      |      |       |

| OTPH                            | Over Temperature Lockout       |                     |            | 145  |      | °C    |

| OTPL                            | Over Temperature Resume        |                     |            | 125  |      | °C    |

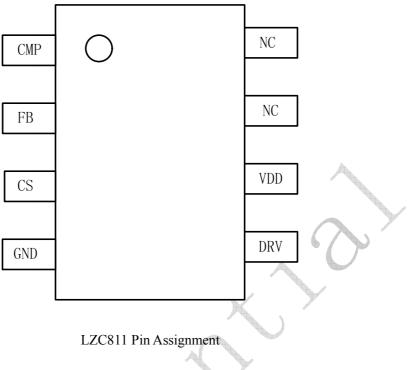

### Operation

The LZC811 is a primary side control offline LED controller that incorporates all the features for high performance LED lighting. LED current can be accurately controlled with the real current control method form the primary side information. Active Power Factor Correction (PFC) is included to eliminate the unwanted harmonic noise injected onto the AC line.

#### Startup

During start-up, the current can charge up the VDD hold capacitor. the turn-on and turn-off thresholds of LZC811 are approximately 15V and 9V respectively. The 6V hysteresis voltage is implemented to prevent shutdown from a voltage dip during start-up.

### Quasi Resonance mode (QRM)

During the external power MOSFET on time  $(T_{ON})$ , the rectified input voltage is applied across the primary side inductor (Lm) and the primary current increases linearly from zero to the peak value (I<sub>PK</sub>). When the external power MOSFET turns off, the energy stored in the inductor forces the secondary side diode to be turn-on, and the current of the inductor begins to decrease linearly from the peak value to zero. When the current decreases to zero, the parasitic resonant of inductor and all the parasitic capacitance makes the power MOSFET drain-source voltage decrease, this decreasing is also reflected on the auxiliary winding. The zero-current detector in FB pin generates the turn on signal of the external MOSFET when the FB voltage is lower than 0.2V and ensures the MOSFET turn on at a valley voltage .

As a result, there are virtually no primary switch turn-on losses and no secondary diode reverse-recover losses. It ensures high efficiency and low EMI noise.

### Active Power Factor Correction (APFC)

LZC811 is designed with quasi-resonance and constant on time  $T_{on}$  to achieve high power factor

under normal operation. The on time of LZC811 vary with input AC voltage  $V_{P}Sin\overline{\omega}t$  and load condition and its value is constant basically because of very large loop compensation capacitance on CMP pin. According to following equations,

$$I_{L-peak} = \frac{V_P Sin \, \overline{o}t}{L_m} \times T_{on} \ I_{L-avg} = \frac{V_P Sin \, \overline{o}t}{2 \times L_m} \times T_{on}^2 \times f_{osc}$$

The peak current  $I_{L-peak}$  and average current  $I_{L-ave}$  of transformer will be shaped as AC input sinusoid too because  $T_{on}$  and  $f_{osc}$  both are constant and then high power factor can be achieved. Preliminary Ver:0.24 Confidential Page 5

### Real Current Regulator without Secondary Feedback

The proprietary real current control method allows the LZC811 to accurately control the secondary side LED current from the primary side information. The output LED mean current can be calculated approximately as:

$$I_{OUT} = \frac{1}{10 \times R_{CS}} \times V_{REF} \times \frac{N_p}{N_s}$$

Where  $I_{OUT}$  is the secondary output current of LED,  $V_{REF}$  is the inner reference voltage.  $N_P$  is number of turns of primary winding and  $N_S$  is number of turns of the secondary winding.

### Auto Starter

The LZC811 integrates an auto starter, the starter starts timing when the MOSFET is turned on, if FB fails to send out another turn on signal after 130µs, the starter will automatically send out the turn on signal which can avoid the IC unnecessary shut down by FB missing detection.

#### Minimal Off Time

The LZC811 operates with variable switching frequency. The frequency is changing with the input instantaneous line voltage. To limit the maximum frequency and get a good EMI performance, LZC811 employs an internal minimum off time limiter—3.5µs, show as figure.

## Leading-Edge Blanking for CS pin

In order to avoid the premature termination of the switching pulse due to the parasitic capacitance discharging at MOSFET turning on, an internal leading edge blanking (LEB) unit is employed between the CS Pin and the current comparator input. During the blanking time, the path, CS Pin to the current comparator input, is blocked. Figure shows the leading edge blanking.

## Output over Voltage Protection

Output over voltage protection can prevent the components from damage in the over voltage condition. The positive plateau of auxiliary winding voltage is proportional to the output voltage. The OVP uses the auxiliary winding voltage instead of directly monitoring the output voltage. Once the FB pin voltage is higher than 3.6V, the OVP signal will be triggered and latched, the gate driver will be turned off and

the IC work at quiescent mode, the VDD voltage dropped below the UVLO which will make the IC shut down and the system restarts again. The output OVP setting point can be calculated as:

$$V_{OUT\_OVP} \approx 3.6 \times \frac{N_S}{N_{AUX}} \times \frac{R_{FBH} + R_{FBL}}{R_{FBL}}$$

$V_{OUT_OVP}$ .....Output over voltage protection value  $N_{AUX}$ .....the auxiliary winding turns  $N_{S}$ .....the secondary winding turns

## Current Limit

The current limit circuit senses the current of inductor by CS pin. When this current exceeds the internal threshold, typical is 1.0V, the power MOSFET is turned off for the remainder of that cycle.

## Leading-Edge Blanking For FB Pin

As shown in Fig, when the power MOSFET is turned off, a damping voltage spike will occur at FB pin due to parasitic capacitance of power MOSFET and leak inductor of transformer. An internal leading edge blanking (LEB) was introduced to filter this noise.

## Output Short Circuit Protection

When the output short circuit happens, the positive plateau of auxiliary winding voltage is also near zero. The IC will shut down and restart again once FB voltage falls below 1.0V and lasts for about 20mS.

## Thermal Shut Down

The thermal shutdown circuitry senses the die temperature. The threshold is set at 150°C typical with a 25°C hysteresis. When the die temperature rises above this threshold (150°C), the 840X turn off the power MOSFET by DRV and remains turning off until the die temperature falls by 25°C, at which point it is re-enabled.

## VDD over Voltage Protection

LZC811 provides an over voltage protection circuit for VDD pin. The GATE output will shut down once the VDD voltage exceeds 25V (typical value), the IC would restart until VDD drops to 9.0V.

## Fault protection

There is several default protections were integrated in the LZC811 to prevent the IC from being damaged which including FB pin open or short, CS pin open.

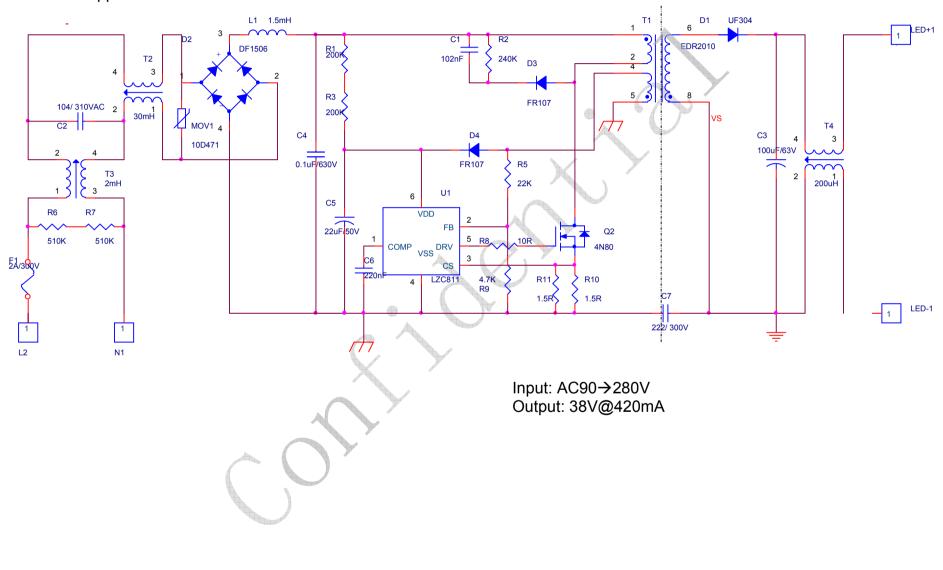

Reference Application Schematic

Preliminary Ver:0.24

ECHNOLOGY INC

Package information

| MBOL | MILLIMETER |      |       |  |  |

|------|------------|------|-------|--|--|

| MBOL | MIN        | NOM  | MAX   |  |  |

| A    | -          |      | 1.75  |  |  |

| A1   | 0.10       | -    | 0.225 |  |  |

| A2   | 1.30       | 1.40 | 1.50  |  |  |

| A3   | 0.60       | 0.65 | 0.70  |  |  |

| D    | 4.70       | 4.90 | 5.10  |  |  |

| Е    | 5.80       | 6.00 | 6.20  |  |  |

| E1   | 3.70       | 3.90 | 4.10  |  |  |

| e    | 1.27BSC    |      |       |  |  |

| h    | h 0.25     |      | 0.50  |  |  |

| L    | 0.50       | _    | 0.80  |  |  |

| LI   | 1.05BSC    |      |       |  |  |

| θ    | 0          |      | 8°    |  |  |

Compliant to JEDEC Standard MS12F

Controlling dimensions are in inches; millimeter dimensions are for reference only

This product is RoHS compliant and Halide free.

Soldering Temperature Resistance: [a] Package is IPC/JEDEC Std 020D Moisture Sensitivity Level 1

[b] Package exceeds JEDEC Std No. 22-A111 for Solder Immersion Resistance; package can withstand 10 s immersion < 270°C

Dimension D does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 mm per end. Dimension E1 does not include inter-lead flash or protrusion. Inter-lead flash or protrusion shall not exceed 0.25 mm per side. D and E1 dimensions are determined at datum H. The package top may be smaller than the package bottom. Dimensions D and E1 are determined at the outer most extremes of the plastic boxy exclusive of mold flash, tie bar burrs, gate burrs and inter-lead flash, but including any mismatch between the top and bottom of the plastic body.

#### Ordering Information

| Part Number | Package | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|-------------|---------|-------------|----------------------------------------|

| LZC811      | SOIC8   | LZC811B     | -40℃~+105℃                             |