## NVM 3060

## Contents

| Page | Section | Title                            |

|------|---------|----------------------------------|

| 3    | 1.      | Introduction                     |

| 4    | 2.      | Specifications                   |

| 4    | 2.1.    | Outline Dimensions               |

| 4    | 2.2.    | Pin Connections                  |

| 4    | 2.3.    | Pin Descriptions                 |

| 5    | 2.4.    | Pin Circuits                     |

| 5    | 2.5.    | Electrical Characteristics       |

| 5    | 2.5.1.  | Absolute Maximum Ratings         |

| 5    | 2.5.2.  | Recommended Operating Conditions |

| 7    | 2.5.3.  | Characteristics                  |

| 8    | 3.      | Functional Description           |

| 8    | 3.1.    | Memory Operation                 |

| 8    | 3.2.    | Testing                          |

| 8    | 3.3.    | Protected Matrix                 |

| 8    | 3.4.    | Shipment                         |

| 9    | 4.      | Test Functions                   |

| 9    | 4.1.    | Block Programming                |

| 9    | 4.2.    | Read Reference Shifting          |

| 9    | 4.3.    | Charge Pump Disable              |

| 10   | 5.      | Description of the IM Bus        |

#### 4096-Bit EEPROM

#### 1. Introduction

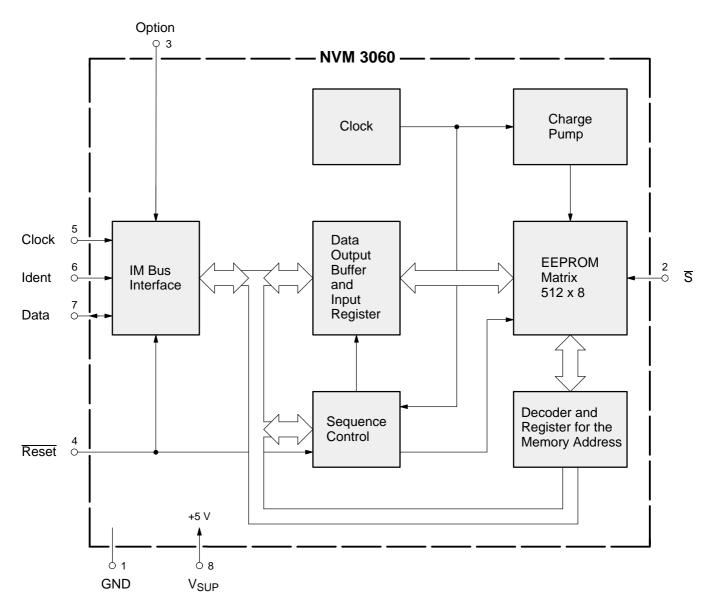

Electrically erasable programmable read-only memory (EEPROM) in N-channel floating-gate technology with a capacity of 512 words, 8 bits each.

The NVM 3060 is intended for use as a reprogrammable non-volatile memory in conjunction with the CCU 2030/2050/2070/3000 series Central Control Units or the SAA 12xx and TVPO 2066 Remote Control and Tuning ICs. It serves for storing the tuning information as

well as several analog settings, further alignment information given in the factory when producing the TV set. The stored information remains stored even with the supply voltages switched off. Reading and programming operations are executed via the IM bus (see section 5.). Input and output signals are TTL level. An address option input provides the possibility to operate two memories in parallel, to obtain a total storage capacity of 8192 bits.

The device contains an on-chip charge pump for high programming voltage generation and an on-chip clock oscillator.

Fig. 1–1: Block diagram of the NVM 3060 EEPROM

## 2. Specifications

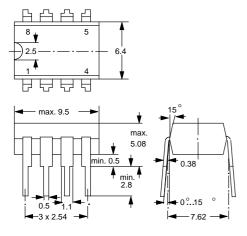

## 2.1. Outline Dimensions

Fig. 2–1: NVM 3060 in 8-pin Dil Plastic Package 20 A 8 according to DIN 41870

Weight approx. 0.5 g

Dimensions in mm

## 2.2. Pin Connections

- 1 Ground, 0

- 2 Safe Input S

- 3 Option Input

- 4 Reset Input

- 5 IM Bus Clock Input

- 6 IM Bus Ident Input

- 7 IM Bus Data Input/Output

- 8 Supply Voltage V<sub>SUP</sub>

### 2.3. Pin Descriptions

Pin 1 – Ground, 0 This pin must be connected to the negative of the supplies.

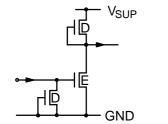

#### Pin 2 – Safe Input S

Fig. 2–2 shows the internal configuration of this input. Normally, with pin 2 at ground potential (low), one portion of the programming matrix is protected so that this part of the memory cannot be reprogrammed inadvertently. Only when pin 2 receives high potential continuously, the protected portion of the memory matrix can be programmed. Pin 2 is internally tied to ground via a transistor equivalent to a 40 k $\Omega$  resistor.

Pin 3 – Option Input Fig. 2–2 shows the internal configuration of this input. With pin 3 at ground potential (low) or floating, the NVM 3060 reacts upon the IM bus addresses 128,129 and 131. With pin 3 continuously at V<sub>SUP</sub> potential (high), the NVM 3060 reacts upon this IM bus addresses 132,133 and 135 (see Fig.2–6). In this way, parallel operation of two NVM 3060 is permitted, to obtain 8192 bits of non-volatile storage directly accessible via the IM bus. Pin 3 is internally tied to ground via a transistor equivalent to a 40 k $\Omega$  resistor.

### Pin 4 - Reset Input

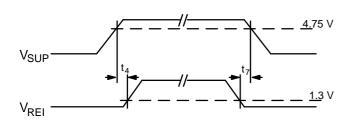

This input has a configuration as shown in Fig. 2–3. Via this input, the NVM 3060, together with the other circuits belonging to the system, receives the Reset signal which is derived from  $V_{SUP}$  via an external RC circuit. A low level is required during power-up and power-down procedures. Low level at pin 4 (max. 1.3 V) cancels a programming procedure and an IM bus operation in progress. The memory address register is not erased. During operation, pin 4 requires high level (min. 2.4 V).

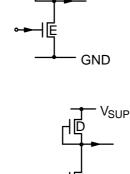

#### Pins 5 to 7 - IM Bus Connections

These pins serve to connect the NVM 3060 EEPROM to the IM bus (see section 5.), via which it communicates with the CCU 2030/2050/2070/3000 Central Control Units or the SAA 12xx and TVPO 2066 Remote Control and Tuning ICs. Pins 5 (IM Bus Clock Input) and 6 (IM Bus Ident Input) are inputs as shown in Fig. 2–3 and pin 7 (IM Bus Data) is an input/output as shown in Fig. 2–4. The signal diagram for the IM bus is illustrated in Figs. 2–6 and Fig. 5–1. The required addresses which the NVM 3060 EEPROM receives from the microcomputer, are also shown in Fig. 2–6.

### Pin 8 – Supply Voltage VSUP

The supply voltage required is +5V ( $\pm5\%$ ), and the current consumption in active operation is approx. 30 mA. Inserting or removing the NVM 3060 from a live socket may alter programmed data!

## NVM 3060

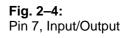

## 2.4. Pin Circuits

The following figures show schematically the circuitry at the various pins. The integrated protection structures are not shown. The letter "E" means enhancement, the letter "D" depletion.

**Fig. 2–2:** Pins 2 and 3, Input S

ł IE

١D

VSUP

GND

Fig. 2–3: Pins 4, 5, and 6, Inputs

#### 2.5. Electrical Characteristics

All Voltages are referred to ground.

#### 2.5.1. Absolute Maximum Ratings

| Symbol           | Parameter                        | Pin No. | Min.   | Max.             | Unit |

|------------------|----------------------------------|---------|--------|------------------|------|

| T <sub>A</sub>   | Ambient Operating<br>Temperature | _       | 0      | 65               | °C   |

| Τ <sub>S</sub>   | Storage Temperature              | _       | -40    | +125*            | °C   |

| V <sub>SUP</sub> | Supply Voltage                   | 8       | -0.5   | +6               | V    |

| VI               | Input Voltage                    | 2 to 7  | –0.3 V | V <sub>SUP</sub> | _    |

| I <sub>O</sub>   | Output Current                   | 7       | _      | 5                | mA   |

\* Stored data may be affected by  $T_S$  above +85  $^\circ\text{C}$

## 2.5.2. Recommended Operating Conditions

| Symbol            | Parameter                                       | Pin No.      | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------------------------------|--------------|------|------|------|------|

| V <sub>SUP</sub>  | Supply Voltage                                  | 8            | 4.75 | 5.0  | 5.25 | V    |

| VIL               | Input Low Voltage                               | 2, 3, 5 to 7 | -    | _    | 0.8  | V    |

| VIH               | Input High Voltage                              |              | 2.4  | _    | _    | V    |

| V <sub>REIL</sub> | Reset Input Low Voltage                         | 4            | -    | _    | 1.3  | V    |

| V <sub>REIH</sub> | Reset Input High Voltage                        |              | 2.4  | _    | _    | V    |

| t <sub>4</sub>    | V <sub>SUP</sub> – V <sub>REI</sub> Delay Time* | 4, 8         | 0    | _    | _    | ms   |

| t <sub>7</sub>    | V <sub>REI</sub> – V <sub>SUP</sub> Delay Time* |              | 0    | _    | _    | ms   |

\*see Fig. 2–5

# NVM 3060

## Recommended Operating Conditions, continued

| Symbol            | Parameter                                                 | Pin No. | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------------------------|---------|------|------|------|------|

| V <sub>IMIL</sub> | IM Bus Input Low Voltage                                  | 5 to 7  | -    | -    | 0.8  | V    |

| V <sub>IMIH</sub> | IM Bus Input High Voltage                                 |         | 2.4  | -    | -    | V    |

| $f_{\Phi I}$      | ΦI IM Bus Clock Frequency                                 |         | 0.05 | -    | 170  | kHz  |

| t <sub>IM1</sub>  | $\Phi$ I Clock Input Delay Time after IM Bus Ident Input  |         | 0    | -    | -    | -    |

| t <sub>IM2</sub>  | ΦI Clock Input<br>Low Pulse Time                          |         | 3.0  | -    | -    | μs   |

| t <sub>IM3</sub>  | ΦI Clock Input<br>High Pulse Time                         |         | 3.0  | -    | -    | μs   |

| t <sub>IM4</sub>  | ΦI Clock Input Setup Time<br>before Ident Input High      |         | 0    | -    | -    | -    |

| t <sub>IM5</sub>  | ΦI Clock Input Hold Time<br>after Ident Input High        |         | 1.5  | -    | -    | μs   |

| t <sub>IM6</sub>  | ΦI Clock Input Setup Time<br>before Ident End-Pulse Input |         | 6.0  | -    | -    | μs   |

| t <sub>IM7</sub>  | IM Bus Input Delay Time<br>after ΦI Clock Input           |         | 0    | -    | -    | -    |

| t <sub>IM8</sub>  | IM Bus Data Input Setup Time before $\Phi$ I Clock Input  |         | 0    | -    | -    | -    |

| t <sub>IM9</sub>  | IM Bus Data Input Hold Time after                         |         | 0    | -    | -    | -    |

| t <sub>IM10</sub> | IM Bus Ident<br>End-Pulse Low Time                        |         | 3.0  | -    | -    | μs   |

Fig. 2-5: Power on/off timing

ITT Semiconductors Group World Headquarters INTERMETALL Hans-Bunte-Strasse 19 D-7800 Freiburg Tel. (0761) 517-0, Telex 772 715 Telefax (0761) 517-174

Printed in Germany by A. Simon & Sohn, Freiburg (2/90) Order No. 6251-309-2E Reprinting is generally permitted, indicating the source. However, our consent must be obtained in all cases. Information furnished by ITT is believed to be accurate and reliable. However, no responsibility is assumed by ITT for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of ITT. The information and suggestions are given without obligation and cannot give rise to any liability; they do not indicate the availability of the components mentioned. Delivery of development samples does not imply any obligation of ITT to supply larger amounts of such units to a fixed term. To this effect, only written confirmation of orders will be binding.