# HT6230 Infrared Remote Encoder

429kHz resonator system clock

(1/2 system frequency and 1/4 duty cycle)

#### **Features**

- Operating voltage: 2.4V~5.2V

- 32 system codes, each system with 64 command codes

- Programmable transmission codes

- · Biphase transmission method

- Generated modulation output data

# **Applications**

- Televisions and video cassette recorder controllers

- Garage door controllers

• Car door controllers

Single pin oscillator

Test pins available

28-pin SOP package

- Security systems

- Other remote control systems

# **General Description**

The HT6230 is designed as infrared remote encoder, usually applied to TV systems. A total of 2048 different commands can be generated and arranged into 32 systems where each system contains 64 different commands. There are 96

keys and to each key is assigned one programmable code. The code is programmable by mask option. Legal and illegal key operation can be distinguished.

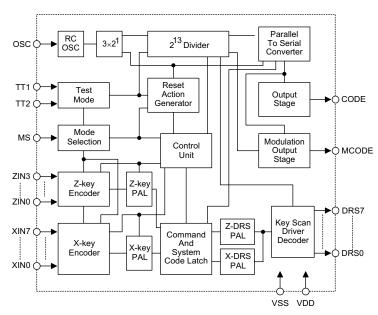

# **Block Diagram**

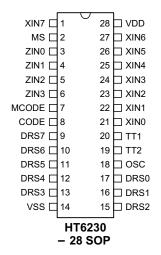

# **Pin Assignment**

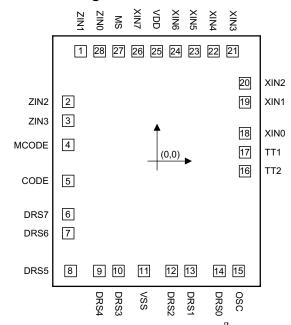

# **Pad Assignment**

$Chip\ size:\ 1605\times1910\ \ \left(\mu m\right)^{2}$  \* The IC substrate should be connected to VDD in the layout artwork.

# **Pad Coordinates**

| U | nit: | μm |

|---|------|----|

|   |      |    |

| Pad No. | X       | Y       | Pad No. | X       | Y       |

|---------|---------|---------|---------|---------|---------|

| 1       | -570.19 | 817.68  | 15      | 605.12  | -817.68 |

| 2       | -662.85 | 442.16  | 16      | 653.07  | -75.59  |

| 3       | -662.85 | 300.74  | 17      | 653.07  | 65.84   |

| 4       | -662.85 | 120.29  | 18      | 653.07  | 207.26  |

| 5       | -662.85 | -147.93 | 19      | 653.07  | 437.29  |

| 6       | -662.85 | -395.02 | 20      | 653.07  | 578.71  |

| 7       | -662.85 | -536.45 | 21      | 561.23  | 817.68  |

| 8       | -644.16 | -817.68 | 22      | 419.80  | 817.68  |

| 9       | -429.58 | -817.68 | 23      | 278.37  | 817.68  |

| 10      | -288.15 | -817.68 | 24      | 136.94  | 817.68  |

| 11      | -98.77  | -817.68 | 25      | -4.48   | 817.68  |

| 12      | 107.68  | -817.68 | 26      | -145.91 | 817.68  |

| 13      | 249.11  | -817.68 | 27      | -287.34 | 817.68  |

| 14      | 463.69  | -817.68 | 28      | -428.76 | 817.68  |

2

# **Pad Description**

| Pad No.   | Pad Name          | I/O | Internal<br>Connection                                   | Description                                                                                |  |

|-----------|-------------------|-----|----------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| 1~3<br>28 | ZIN1~ZIN3<br>ZIN0 | I   | CMOS with<br>PMOS Pull-high                              | Detect inputs from Z-key matrix                                                            |  |

| 4         | MCODE             | О   | Tri-state<br>CMOS                                        | Generate modulation output data code with 1/12 system frequency and 1/4 duty cycle         |  |

| 5         | CODE              | О   | Tri-state<br>CMOS                                        | Generates output data code                                                                 |  |

| 6~10      | DRS7~DRS3         | О   | Open Drain<br>NMOS                                       | Drive for key scanning                                                                     |  |

| 11        | VSS               | _   | _                                                        | Negative power supply, ground                                                              |  |

| 12~14     | DRS2~DRS0         | О   | Open Drain<br>NMOS                                       | Drive for key scanning                                                                     |  |

| 15        | osc               | I   | CMOS                                                     | Oscillator input                                                                           |  |

| 16~17     | TT2~TT1           | I   | CMOS                                                     | Switch to four operating modes: 0 0 normal mode 0 1 test mode 1 1 0 test mode 2 1 1 Reset  |  |

| 18~24     | XIN0~XIN6         | I   | CMOS with PMOS Pull-high Detect inputs from X-key matrix |                                                                                            |  |

| 25        | VDD               | _   | _                                                        | Positive power supply                                                                      |  |

| 26        | XIN7              | I   | CMOS with PMOS Pull-high Detect input from X-key matrix  |                                                                                            |  |

| 27        | MS                | I   | CMOS                                                     | Select system mode (Two modes provided:<br>One-key system mode and Two-key system<br>mode) |  |

3

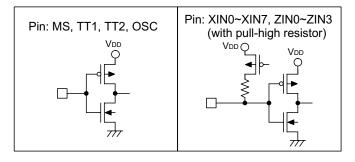

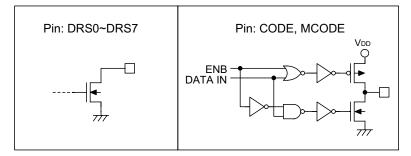

# Approximate internal connection circuits

• Input terminal

### • Output terminal

# **Absolute Maximum Ratings**

| Supply Voltage0.3V to 5.5V                     | Storage Temperature $-50^{\circ}\mathrm{C}$ to $125^{\circ}\mathrm{C}$ |

|------------------------------------------------|------------------------------------------------------------------------|

| Input Voltage $V_{SS}$ -0.3V to $V_{DD}$ +0.3V | Operating Temperature25°C to 75°C                                      |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

### **Electrical Characteristics**

Ta=25°C

| Comple al          | Parameter                              | Test Conditions            |                                      | Min.                 | Т    | М    | TT *4 |

|--------------------|----------------------------------------|----------------------------|--------------------------------------|----------------------|------|------|-------|

| Symbol             | Parameter                              | $\mathbf{V}_{\mathbf{DD}}$ | Conditions                           | Wiin.                | Тур. | Max. | Unit  |

| $V_{\mathrm{DD}}$  | Supply Voltage                         |                            | _                                    | 2.4                  | _    | 5.2  | V     |

| $V_{\mathrm{OL1}}$ | DRS0~DRS7 Output<br>Voltage Low        | 3V                         | I <sub>OL1</sub> =0.3mA              |                      |      | 0.3  | V     |

| $V_{ m OL2}$       | CODE, MCODE Output<br>Voltage Low      | 3V                         | I <sub>OL2</sub> =0.6mA              | _                    | _    | 0.3  | V     |

| V <sub>OH</sub>    | CODE, MCODE Output<br>Voltage High     | 3V                         | I <sub>OH</sub> =-0.4mA              | V <sub>DD</sub> -0.3 | _    | _    | V     |

| $R_{PH}$           | XIN0~XIN7 and<br>ZIN0~ZIN3 Pull-high   | 3V                         | TT1=TT2=MS=Low<br>V <sub>I</sub> =0V | _                    | 27   | _    | kΩ    |

| $f_{ m OSC}$       | Oscillator Frequency<br>Operational 3V |                            | _                                    | _                    | 429  | _    | kHz   |

| TOSC               | Free-running                           | v                          | _                                    | 30                   | 50   | 100  | kHz   |

## **Functional Description**

#### **Key operation**

When MS is low, the legal key operation is that only one ZIN or XIN can be connected to one DRS driver and if more than one XIN, ZIN or both are pressed at the same time then the key operation is recognized as illegal; hence, the oscillator will not start. When MS is high, the legal key operation is that exactly one ZIN and one XIN are connected to two DRS drivers and other cases of key operation are all considered as illegal.

However, when one XIN or ZIN is connected to more than one DRS, the last key scan driver is to generate output data code.

#### Format of transmission code

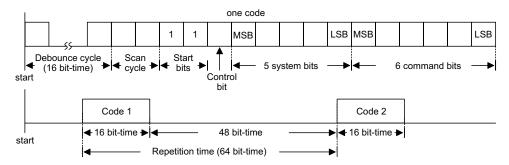

The output pin CODE transmits the data code as a code format, as shown at the bottom figure.

The method of transmitting one code bit is called biphase transmission and is represented by the following fig:

Where one code bit time is  $3\times2^8\times T_{OSC}$ . The output signal of the MCODE pin is the signal of the generated output code modulated by 1/12 of the system frequency with 1/4 duty cycle. In quies-

cent state both CODE and MCODE are high impedance.

#### Key scan drivers

The key scan drivers DRS0 to DRS7 are open drain NMOS and the outputs of these are all low in quiescent state. When a legal key operation is detected, the debounce cycle starts and at the end of the debounce cycle, the DRS outputs are high impedance. Furthermore, the scanning cycle starts and DRS outputs take turns to switch to low state.

#### Programmable output data code

The output data code corresponding to each key is programmable by hardware mask option. The PAL circuit is necessary for this purpose.

#### **Operation mode**

• One-key system mode

The device enters this mode by switching the MS input pin to low state. The pull-high resistors are connected to all XIN and ZIN inputs so that all sense inputs are at high state, until pulled to low state by key operation. In this mode the legal key operation is that only one ZIN or XIN can be connected to one DRS. When a sense input detects a low level, an enable signal is generated to latch the system or command latches. If the sense input belongs to ZIN, the corresponding system code is generated and the command code is defined as all

Transmission code format

5

logic 1. If the sense input comes from XIN, the corresponding command code together with the system code stored in the system latches are generated.

• Two-key system mode

The device goes into this mode by switching the MS input pin to high state. The pull-high resistors are only connected to XIN inputs except the first scan cycle. In the first scan cycle, there only exists pull-high resistors in ZIN inputs. In this mode, the legal key operation is that exactly one XIN and one ZIN are connected to two DRS drivers. In the first scan duration, it detects which key in Z-key matrix is pressed and generates an enable signal to latch the system latches. While in the second scan duration, it detects which key in the X-key matrix is pressed and generates an enabled signal to latch the command latches. After being latched, the system and command codes are transmitted.

#### **Control bit**

A control bit is added after two start bits and will be complemented if one key is released. The decoder can decide whether the next code is a new command or not.

#### Oscillator

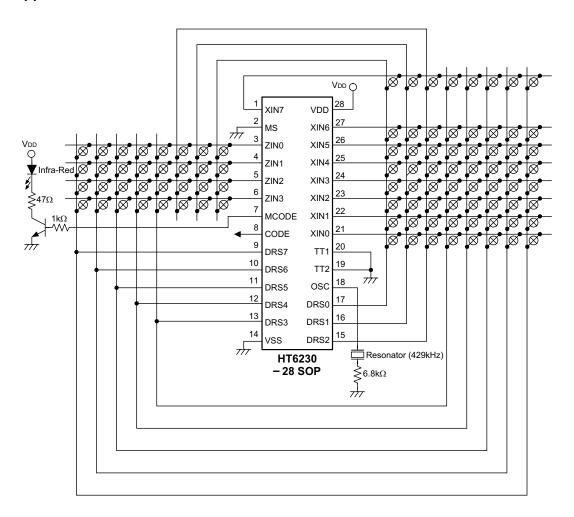

The embedded part of the oscillator is an RC-oscillation circuit. The OSC pin is the input terminal of the RC-oscillation circuit and is connected to an external ceramic resonator (429kHz). A resistor of  $6.8 \mathrm{k}\Omega$  must be in series with the resonator. The resonator and resistor are grounded at one side.

### Reset (after key release)

In a complete code repetition time, as shown in the figure below, the following situation of key release results in a reset action.

6

- During Tsep and debounce time, the device will reset immediately if a key is released.

- During Scan cycle in Tcode, a reset will occur if a key is released in three cases described below:

- When one of the key scan drivers is in the low state

- Before that key has been detected

- When MS is high and there is no wired connection in Z-key matrix

#### Test pins (TT1 and TT2)

There are four modes by the combination of TT1 and TT2.

| TT1 | TT2 | Mode        |

|-----|-----|-------------|

| 0   | 0   | Normal mode |

| 1   | 1   | Reset       |

| 1   | 0   | Test mode 1 |

| 0   | 1   | Test mode 2 |

# **Application Circuits**

where

$$\stackrel{\blacklozenge}{\bigoplus} \equiv \stackrel{\lozenge}{\lozenge}$$

push-button switch

### Holtek Semiconductor Inc. (Headquarters)

No.3 Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan, R.O.C.

Tel: 886-3-563-1999 Fax: 886-3-563-1189

#### Holtek Semiconductor Inc. (Taipei Office)

5F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan, R.O.C.

Tel: 886-2-2782-9635 Fax: 886-2-2782-9636

$Fax: 886\text{-}2\text{-}2782\text{-}7128 \ (International \ sales \ hotline)$

#### Holtek Semiconductor (Hong Kong) Ltd.

RM.711, Tower 2, Cheung Sha Wan Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong Kong

Tel: 852-2-745-8288 Fax: 852-2-742-8657

### Copyright © 2000 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.