CMOS SINGLE-COMPONENT 8-BIT MICROCOMPUTER

#### **Description**

The AUK 60C31/P 60C51/P is a high-performance micro controller fabricated with AUK high-density CMOS technology. The AUK CMOS technology combines the high speed and density characteristics of MOS with the low power attributes of CMOS.

The 60C51 contains a 4K x 8 ROM, a 128 x 8 RAM, 32 I/O lines, two 16-bit counter/timers, a five-source, two-priority level nested interrupt structure, a serial I/O port for either multiprocessor communication, I/O expansion or full duplex UART, and on-chip oscillator and clock circuits.

In addition, the device has two software selectable modes of power reduction idle mode and power-down mode. The idle mode freezes the CPU while allowing the RAM, timers, serial port, and interrupt system to continue functioning.

#### **Features**

- 8-bit CPU optimized for control applications.

- Pin-to-pin compatible with intel's 80C51/80C31.

- 60C51 low power mask programmable ROM

- 64K Program Memory Space, Data Memory space

- 32K programmable I/O lines.

- High performance CMOS process.

- 2 Level programmable serial port

- Power control modes.

- 60C31 low power CPU only

- ce

Two 16bit timer/counters

- 5 interrupt sources.

- 3.5 to 12MHz @ 5V  $\pm$  20%

**Ordering Information**

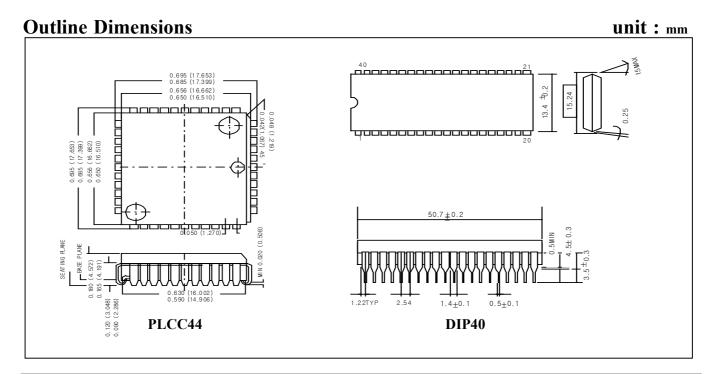

| Type NO. | Marking | Package Code | Type NO. | Marking | Package Code |

|----------|---------|--------------|----------|---------|--------------|

| SD60C31  | SD60C31 | PLCC44       | SD60C31P | SD60C31 | DIP40        |

| SD60C51  | SD60C51 | PLCC44       | SD60C51P | SD60C51 | DIP40        |

### **Absolute Maximum Ratings**

| Characteristic                      | Rating         | Unit |  |

|-------------------------------------|----------------|------|--|

| Ambient temperature under bias      | 0 ~+70         | °C   |  |

| Storage temperature                 | -65 ~ +150     | °C   |  |

| Voltage on any pin to Vss           | -0.5~Vcc + 0.5 | V    |  |

| Maximum I <sub>OL</sub> per I/O pin | 15             | mA   |  |

| Power dissipation                   | 1              | Watt |  |

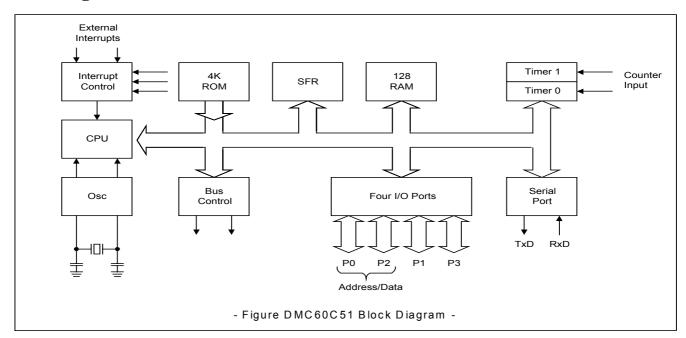

#### **Block Diagram**

### **Description**

The AUK 60C31/P 60C51/P is a high-performance micro controller fabricated with AUK high-density CMOS technology. The AUK CMOS technology combines the high speed and density characteristics of MOS with the low power attributes of CMOS.

The 60C51 contains a 4K×8 ROM, a 128×8 RAM, 32I/O lines, two 16-bit counter/times, a five-source, two-priority level nested interrupt structure, a serial I/O port for either multi-processor communication, I/O expansion or full duplex UART, and on-chip oscillator and clock circuists.

In addition, the device has tow software selectable modes of power reduction idle mode and powerdown mode. The idle mode freezes the CPU while allowing the RAM, times, serial port, and interrupt system to continue functioning.

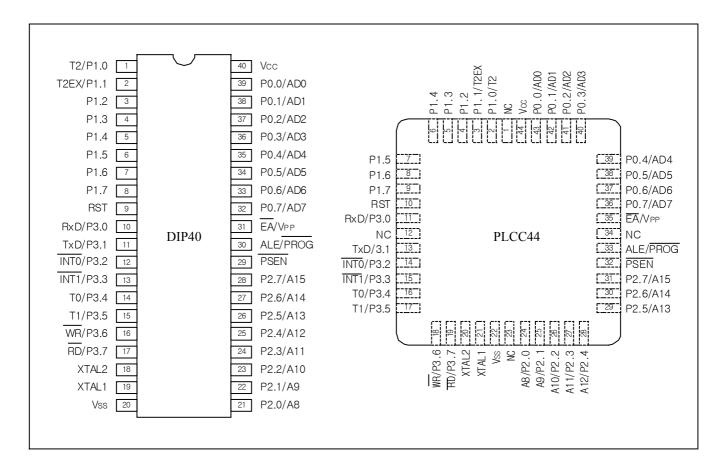

### **Pin Configuration**

### **Pin Description**

V<sub>CC</sub> : PIN 40 (DIP40), PIN 44 (PLCC44)

Supply voltage during normal, Idle and power down operations.

V<sub>SS</sub> : PIN 20 (DIP40), PIN 22 (PLCC44)

Circuit ground.

Port 0 : PIN 32~39 (DIP40), PIN 36~43 (PLCC44)

Port 0 is an 8bit open drain bi-directional I/O port. Port 0 pins that have 1's written to the them float, and in that state can be used as high impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory.

In this application it uses strong internal pullups when emitting 1's.

#### **Pin Description(continued)**

Port 1 : PIN 1~8 (DIP40), PIN 2~9 (PLCC44)

Port 1 is an 8-bit bi-directional I/O port with internal pullups.

Port 1 pins that have 1's written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current because of the internal pullups.

#### Port 2 : PIN 21~28 (DIP40), PIN 24~31 (PLCC44)

Port 2 is an 8-bit bi-directional I/O port with internal pullups. Port 2 pins that have 1's written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current because of the internal pullups.

Port 2 emits the high-order address byte during fetches from external Program Memory and during accesses to external Data Memory that use 16-bit addresses (MOVX @ DPTR). In this application it uses strong internal pullups when emitting 1's. During accesses to external data memory that use 8-bit addresses (MOVX @ Ri), Port 2 emits the contents of the P2 Special Function Register

#### Port 3 : PIN 10~17 (DIP40), PIN 13~19 (PLCC44)

Port 3 is an 8-bit bi-directional I/O port with internal pullups. Port 3 pins that have 1's written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current because of the pullups.

Port 3 also serves the function of various special feature of the MCS-51 Family, as listed below :

| Port PIN | PIN NO.   | Alternate Function                     |

|----------|-----------|----------------------------------------|

| P3.0     | <u>10</u> | RxD (Serial input port)                |

| P3.1     | 11        | TxD (Serial output port)               |

| P3.2     | 12        | INTO (external interrupt 0)            |

| P3.3     | 13        | INT1 (external interrupt 1)            |

| P3.4     | 14        | T0 (Timer 0 external input)            |

| P3.5     | 15        | T1 (Timer 1 external input)            |

| P3.6     | 16        | WR (external data memory write strobe) |

| P3.7     | 17        | RD (external data memory read strobe)  |

#### RST : PIN 9 (DIP40), PIN 10 (PLCC44)

Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device. An internal diffused resistor to  $V_{\text{SS}}$  permits Power-On reset using only an external capacitor to  $V_{\text{CC}}$ .

#### **Pin Description(continued)**

ALE : PIN 30 (DIP40), PIN 33 (PLCC44)

Address latch enable output pulse for latching the low byte of the address during accesses to external memory.

In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing of clocking purposes.

Note: However, that one ALE pulse is skipped during each access to external data memory.

If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH.

With the bit set, ALE is active only during a MOVX instruction. Otherwise, the pin is weakly pulled high.

PSEN : PIN 29 (DIP40), PIN 32 (PLCC44)

Program store enable is the read strobe to external program memory. When the 60C51 is executing code from external program memory,  $\overline{\text{PSEN}}$  is activated twice each machine cycle, except that two  $\overline{\text{PSEN}}$  activations are skipped during each access to external data memory.  $\overline{\text{PSEN}}$  is not activated during fetches from internal program memory.

EA : PIN 31 (DIP40), PIN 35 (PLCC44)

External access enable.  $\overline{\text{EA}}$  must be strapped to  $V_{SS}$  in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH.

If  $\overline{EA}$  is strapped to  $V_{CC}$  the device executes from internal program memory unless the program counter contains an address greater than 0FFFH.

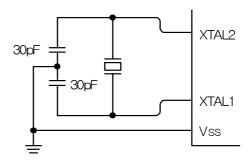

XTAL1 : PIN 19 (DIP40), PIN 21 (PLCC44)

Input to the inverting oscillator amplifier and input to the internal clock generator circuits.

NC : PIN1, 12, 23, 34 (PLCC44)

Non connection pins.

XTAL2 : PIN 18 (DIP40), PIN 20(PLCC44)

Output from the inverting oscillator amplifier

#### **Pin Description(continued)**

Crystal oscillator

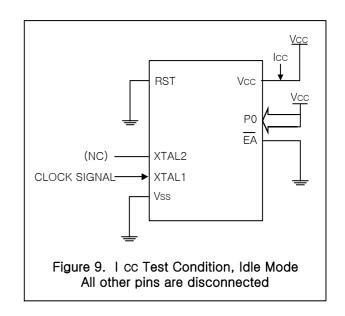

#### **Idle Mode**

In the Idle mode, the CPU puts itself to sleep while all the on chip peripherals stay active. The instruction that invokes the Idle mode is the last instruction executed in the normal operating mode before Idle mode is activated.

The content of the on-chip RAM and all the special function registers remain intact during this mode. The Idle mode can be terminated either by any enabled interrupt, at which time the process is picked up at the interrupt service routine and continued, or by a hardware reset which starts the processor the same as a power on reset.

#### **Power Down Mode**

In the power down mode the oscillator is stopped, and the instruction that invokes power down is the last instruction executed. The on-chip RAM and special function register retain their values until the power down mode is terminated.

The only exit from power down is a hardware reset. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before  $V_{CC}$  is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize.

The control bits for the reduced power modes are in the special function register PCON.

Table Status of the external pins during Idle and power down modes.

| Mode       | Program<br>memory | ALE | PSEN | PORT 0 | PORT 1 | PORT 2  | PORT 3 |

|------------|-------------------|-----|------|--------|--------|---------|--------|

| Idle       | Internal          | 1   | 1    | Data   | Data   | Data    | Data   |

| Idle       | External          | 1   | 1    | Float  | Data   | Address | Data   |

| Power down | Internal          | 0   | 0    | Data   | Data   | Data    | Data   |

| Power down | External          | 0   | 0    | Float  | Data   | Data    | Data   |

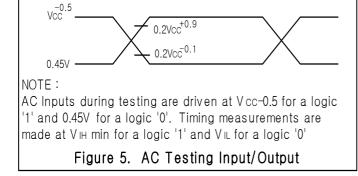

Electrical Characteristics(DC)  $(T_A = 0 \, \text{°C} \sim 70 \, \text{°C} \text{ or } -40 \, \text{°C} \sim 85 \, \text{°C}, V_{CC} = 5V \pm 20\%, V_{SS} = 0V)$

| SYMBOL             | PARAMETER                                                                           | TEST                                                                |                                                  | UNIT           |                             |                |

|--------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------|----------------|-----------------------------|----------------|

| SIMBOL             | FARAMETER                                                                           | CONDITIONS                                                          | MIN                                              | TYP.           | MAX                         | UNII           |

| $V_{\mathrm{IL}}$  | Input low voltage, except EA                                                        |                                                                     | -0.5                                             |                | 0.2V <sub>CC</sub> -<br>0.1 | V              |

| $V_{\mathrm{ILI}}$ | Input low voltage to EA                                                             |                                                                     | 0                                                |                | 0.2V <sub>CC</sub> -<br>0.3 | V              |

| $V_{\mathrm{IH}}$  | Input high voltage, except XTAL1,RST                                                |                                                                     | 0.2V <sub>CC</sub> +<br>0.9                      |                | V <sub>CC</sub> +0.5        | V              |

| $V_{\mathrm{IHI}}$ | Input high voltage to XTAL1, RST                                                    |                                                                     | 0.7 V <sub>CC</sub>                              |                | V <sub>CC</sub> +0.5        | V              |

| V <sub>OL</sub>    | Output low voltage to ports 1,2,3                                                   | $I_{\text{OL}} = 1.6 \text{ mA}$                                    |                                                  |                | 0.45                        | V              |

| V <sub>OLI</sub>   | Output low voltage to ports 0, ALE, PSEN                                            | $I_{\text{OL}}{=}3.2~\text{mA}$                                     |                                                  |                | 0.45                        | V              |

| $V_{OH}$           | Output high voltage to ports 1,2,3,ALE,PSEN                                         | $I_{OH} = -60 \mu A$ $I_{OH} = -25 \mu A$ $I_{OH} = -10 \mu A$      | 2.4<br>0.75V <sub>cc</sub><br>0.9V <sub>cc</sub> |                |                             | V              |

| $V_{OHI}$          | Output high voltage (port 0 in external bus mode)                                   | $I_{OH} = -800  \mu A$ $I_{OH} = -300  \mu A$ $I_{OH} = -80  \mu A$ | 2.4<br>0.75V <sub>CC</sub><br>0.9V <sub>CC</sub> |                |                             | V              |

| ${ m I}_{ m IL}$   | Logical 0 input current to ports 1,2,3                                              | V <sub>IN</sub> =0.45V                                              |                                                  |                | -50                         | μΑ             |

| $I_{TL}$           | Logical 1 to 0 transition current to port 1,2,3                                     | $V_{IN}=2V$                                                         |                                                  |                | -650                        | μΑ             |

| $\mathbf{I}_{LI}$  | Input <u>lea</u> kage current to port 0, EA                                         | 0.45 <v<sub>IN&lt; V<sub>CC</sub></v<sub>                           |                                                  |                | ±10                         | μА             |

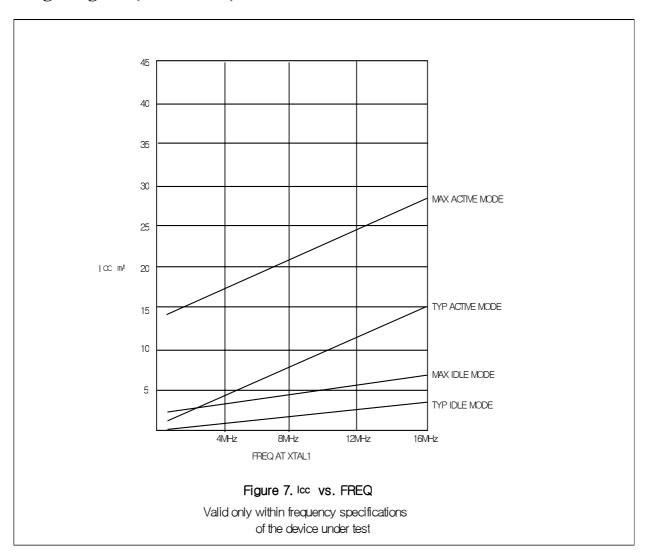

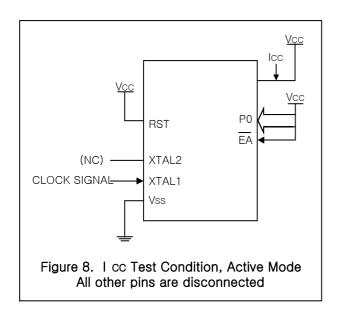

| $\mathbf{I}_{CC}$  | Power supply current<br>Active mode @ 12MHz<br>Idle mode @ 12MHz<br>Power-down mode | See note1                                                           |                                                  | 11<br>1.7<br>5 | 20<br>5<br>50               | mA<br>mA<br>μA |

| R <sub>RST</sub>   | Internal reset pull-down resistor                                                   |                                                                     | 50                                               |                | 150                         | kohm           |

| C <sub>10</sub>    | Pin capacitance                                                                     |                                                                     |                                                  |                | 10                          | pF             |

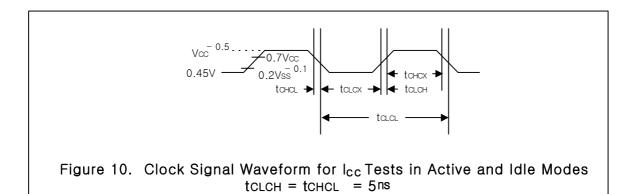

Note : 1. See figure 8 through 11 for  $I_{CC}$  test conditions. Minimum  $V_{CC}$  for power down is 2V.

KSI-W001-000

### **Electrical AC Characteristics(AC)**

(T\_A = 0 °C or -40 °C  $\sim 85$  °C,  $V_{CC}$  = 5V  $\pm$  20%,  $V_{SS}$ =0V)

| SYM                          | FIGU           | PARAMETER                                         |     | MHz<br>OCK | VARIABLE CLOCK          |                         | UNIT |

|------------------------------|----------------|---------------------------------------------------|-----|------------|-------------------------|-------------------------|------|

| -BOL                         | RE             |                                                   | MIN | MAX        | MIN                     | MAX                     |      |

| 1/t <sub>CLC</sub>           |                | Oscillator frequency : Speed versions 60C31/60C51 |     |            | 3.5                     | 12                      | MHz  |

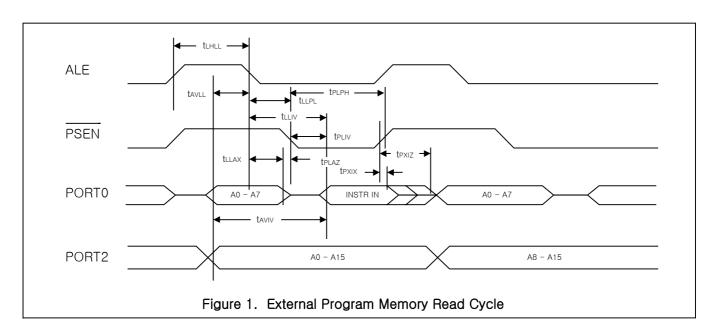

| t <sub>LHLL</sub>            | 1              | ALE pulse width                                   | 127 |            | 2t <sub>CLCL</sub> -40  |                         | ns   |

| t <sub>AVLL</sub>            | 1              | Address valid to ALE low                          | 28  |            | $t_{CLCL}$ -55          |                         | ns   |

| t <sub>LLAX</sub>            | 1              | Address hold after ALE low                        | 48  |            | t <sub>CLCL</sub> -35   |                         | ns   |

| $t_{LLIV}$                   | 1              | ALE low to valid instruction in                   |     | 234        |                         | 4t <sub>CLCL</sub> -100 | ns   |

| $t_{\scriptscriptstyleLLPL}$ | 1              | ALE low to PSEN low                               | 43  |            | $t_{CLCL}$ -40          |                         | ns   |

| t <sub>PLPH</sub>            | 1              | PSEN pulse width                                  | 205 |            | 3t <sub>CLCL</sub> -45  |                         | ns   |

| $t_{PLIV}$                   | 1              | PSEN low to valid instruction in                  |     | 145        |                         | 3 <sub>CLCL</sub> -105  | ns   |

| t <sub>PXIX</sub>            | 1              | Input instruction hold after PSEN                 | 0   |            | 0                       |                         | ns   |

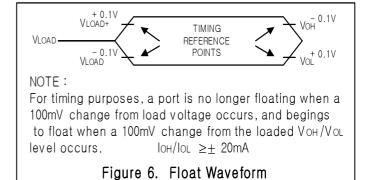

| $t_{PXIZ}$                   | 1              | Input instruction float after PSEN                |     | 59         |                         | t <sub>CLCL</sub> -25   | ns   |

| t <sub>AVIV</sub>            | 1              | Address to valid instruction in                   |     | 312        |                         | 5t <sub>CLCL</sub> -105 | ns   |

| t <sub>PLAZ</sub>            | 1              | PSEN low to address float                         |     | 10         |                         | 10                      | ns   |

| Data M                       | <b>1</b> emory |                                                   |     |            |                         |                         |      |

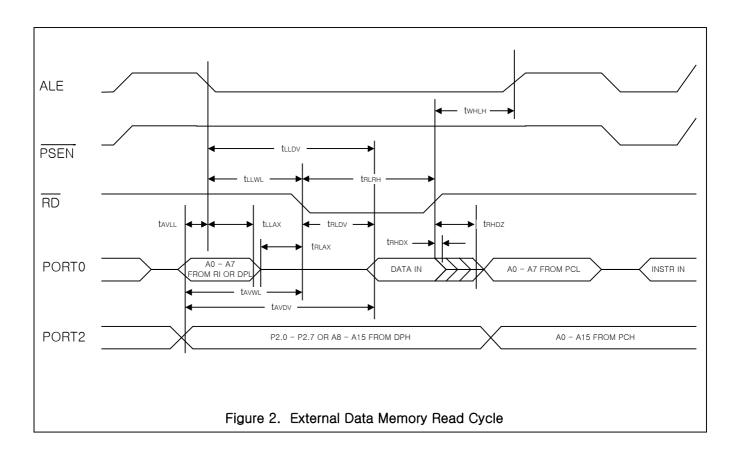

| t <sub>RLRH</sub>            | 2.3            | RD pulse width                                    | 400 |            | 6t <sub>CLCL</sub> -100 |                         | ns   |

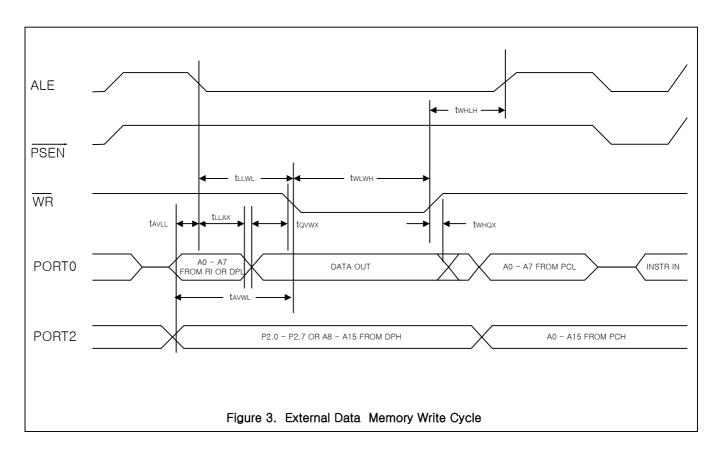

| t <sub>wLWH</sub>            | 2.3            | WR pulse width                                    | 400 |            | 6t <sub>CLCL</sub> -100 |                         | ns   |

| $t_{RLDV}$                   | 2.3            | RD low to valid data in                           |     | 252        |                         | 5t <sub>CLCL</sub> -165 | ns   |

| $t_{RHDX}$                   | 2.3            | Data hold after RD                                | 0   |            | 0                       |                         | ns   |

| $t_{RHDZ}$                   | 2.3            | Data float after RD                               |     | 97         |                         | 2t <sub>CLCL</sub> -70  | ns   |

| $t_{LLDV}$                   | 2.3            | ALE low to valid data in                          |     | 517        |                         | 8t <sub>CLCL</sub> -150 | ns   |

| t <sub>AVDV</sub>            | 2.3            | Address to valid data in                          |     | 585        |                         | 9t <sub>CLCL</sub> -165 | ns   |

| $t_{LLWL}$                   | 2.3            | ALE low to RD or WR low                           | 200 | 300        | $3t_{CLCL}$ -50         | 3t <sub>CLCL</sub> +50  | ns   |

| t <sub>AVWL</sub>            | 2.3            | Address valid to WR low or RD low                 | 203 |            | 4t <sub>CLCL</sub> -130 |                         | ns   |

| $t_{QVWX}$                   | 2.3            | Data valid to WR transition                       | 23  |            | $t_{CLCL}$ -60          |                         | ns   |

| $t_{\text{WHQZ}}$            | 2.3            | Data hold after WR                                | 33  |            | $t_{CLCL}$ -50          |                         | ns   |

| t <sub>RLAZ</sub>            | 2.3            | RD low to address float                           |     | 0          |                         | 0                       | ns   |

| t <sub>whlh</sub>            | 2.3            | RD or WR high to ALE high                         | 43  | 123        | t <sub>CLCL</sub> -40   | t <sub>CLCL</sub> +40   | ns   |

| Extern                       | al Clock       | K                                                 |     |            |                         |                         |      |

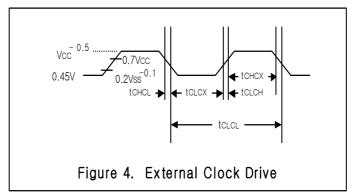

| t <sub>CHCX</sub>            | 4              | High time                                         | 20  |            | 20                      |                         | ns   |

| t <sub>CLCX</sub>            | 4              | Low time                                          | 20  |            | 20                      |                         | ns   |

| t <sub>CLCH</sub>            | 4              | Rise time                                         |     | 20         |                         | 20                      | ns   |

| t <sub>CHCL</sub>            | 4              | Fall time                                         |     | 20         |                         | 20                      | ns   |

## **Timing Diagram**

### **Timing Diagram(Continued)**

### **Timing Diagram(Continued)**

### **Timing Diagram(Continued)**

RST Vcc PO EA Vcc PO EA TAL1 Vss Figure 11. Icc Test Condition, Power down Mode All other pins are disconnected, Vcc 2V to 5.5V